You are here:

MIPI I3C Controller and Target fully featured IP solution

The MIPI I3C Controller IP is a highly optimized and technology-agnostic implementation of the MIPI I3C

v.1.1.1 standard targeting both ASIC and FPGA technologies. The Chip Interfaces MIPI I3C IP is used to connect multiple Targets to one or more Controllers with Secondary controllers having the capability to take ownership of the bus. The IP can act as the Bus Controller or Secondary Controller with the inclusion of the Target Engine, it is also possible to set up as a simple Target or Composite Device with multiple Virtual Targets. The MIPI I3C IP from Chip Interfaces supports SDR and HDR transmission modes over a single or multiple lanes allowing it to reach transfer speeds of up to 100 Mbps.

The Chip Interfaces MIPI I3C Controller IP is backwards compatible with MIPI I3C versions 1.1 and 1.0, as well

as with I2C. The Application data interface follows the TCRI v1.0 specification.

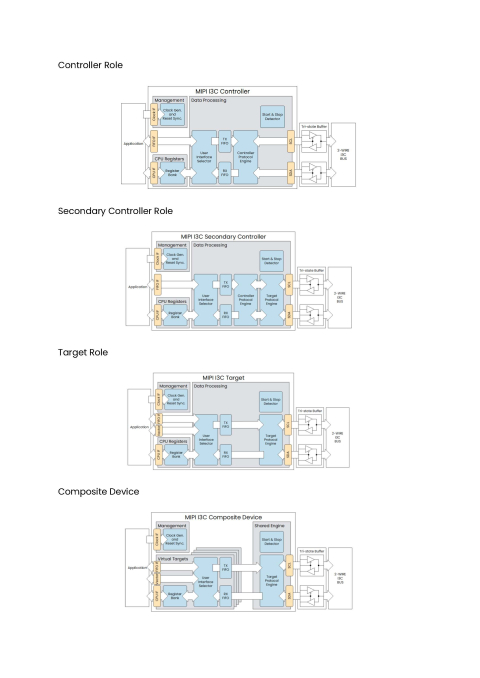

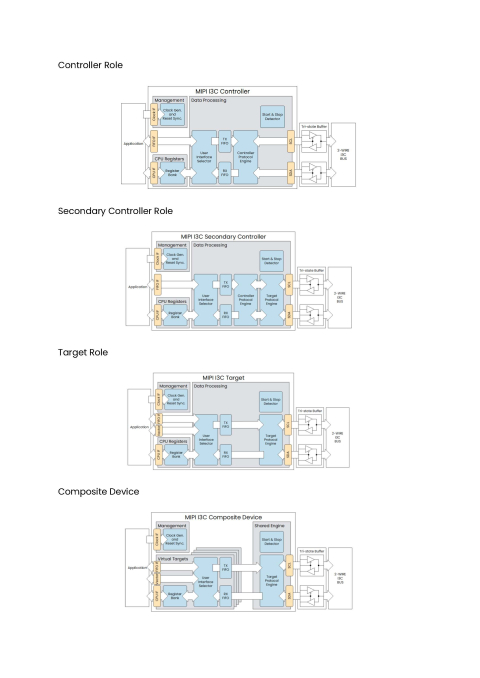

IP Roles :

The IP Core can be configured to fulfil one of several roles on the I3C Bus:

Controller – Always Active Bus Controler

Secondary Controller – Bus Controler capable of handing over the Role and active as Target

Target – Acting only as the target device on the bus

Composite Device – Capable of instantiating multiple Virtual targets

v.1.1.1 standard targeting both ASIC and FPGA technologies. The Chip Interfaces MIPI I3C IP is used to connect multiple Targets to one or more Controllers with Secondary controllers having the capability to take ownership of the bus. The IP can act as the Bus Controller or Secondary Controller with the inclusion of the Target Engine, it is also possible to set up as a simple Target or Composite Device with multiple Virtual Targets. The MIPI I3C IP from Chip Interfaces supports SDR and HDR transmission modes over a single or multiple lanes allowing it to reach transfer speeds of up to 100 Mbps.

The Chip Interfaces MIPI I3C Controller IP is backwards compatible with MIPI I3C versions 1.1 and 1.0, as well

as with I2C. The Application data interface follows the TCRI v1.0 specification.

IP Roles :

The IP Core can be configured to fulfil one of several roles on the I3C Bus:

Controller – Always Active Bus Controler

Secondary Controller – Bus Controler capable of handing over the Role and active as Target

Target – Acting only as the target device on the bus

Composite Device – Capable of instantiating multiple Virtual targets

查看 MIPI I3C Controller and Target fully featured IP solution 详细介绍:

- 查看 MIPI I3C Controller and Target fully featured IP solution 完整数据手册

- 联系 MIPI I3C Controller and Target fully featured IP solution 供应商

Block Diagram of the MIPI I3C Controller and Target fully featured IP solution