You are here:

MIPI HSI Controller IP Core

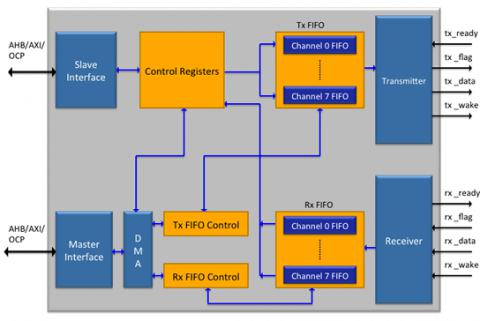

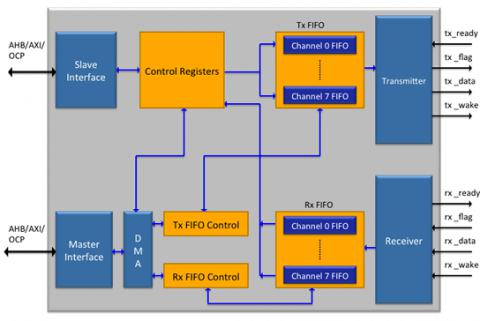

The MIPI HSI Controller IP Core is used to provide high bandwidth, point-to-point, MIPI HSI ver 1.0 compliant serial communication between two peers, like the cellular modem and application processor on a mobile platform, such as a smartphone or a tablet.

Three flavors of the IP are currently available, namely, with support for AHB, AXI or OCP system buses. The IP’s internal registers are accessible through programmed IO transactions, in which case the IP functions as a bus slave. All data transfers between the SoC’s system memory and HSI interface happen either in PIO mode or in DMA mode as programmed by the driver/firmware.

Three flavors of the IP are currently available, namely, with support for AHB, AXI or OCP system buses. The IP’s internal registers are accessible through programmed IO transactions, in which case the IP functions as a bus slave. All data transfers between the SoC’s system memory and HSI interface happen either in PIO mode or in DMA mode as programmed by the driver/firmware.

查看 MIPI HSI Controller - (High-Speed Synchronous Serial Interface) 详细介绍:

- 查看 MIPI HSI Controller - (High-Speed Synchronous Serial Interface) 完整数据手册

- 联系 MIPI HSI Controller - (High-Speed Synchronous Serial Interface) 供应商

Block Diagram of the MIPI HSI Controller - (High-Speed Synchronous Serial Interface)

silicon IP IP

- TSMC GF Intel Samsung Deskew Frequency Synthesizer PLL

- TSMC GF Intel Samsung Fractional-N Frequency Synthesizer PLL

- TSMC GF Intel Samsung Integer-N Frequency Synthesizer PLL

- Jitter Cleaner PLL Digital Loop Filter

- TSMC Intel 32kHz Low-bandwidth Frequency Synthesizer PLL

- The SST SuperFlash® IP is an embedded CMOS Flash memory IP with sector/chip Erase and byte Program capability.