You are here:

MIPI DSI-2 Transmit Controller v1.0

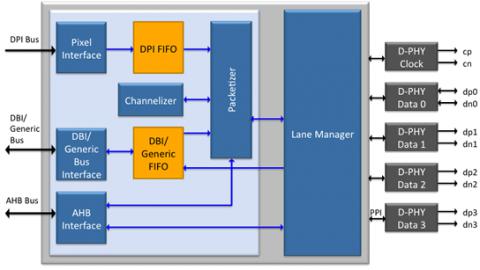

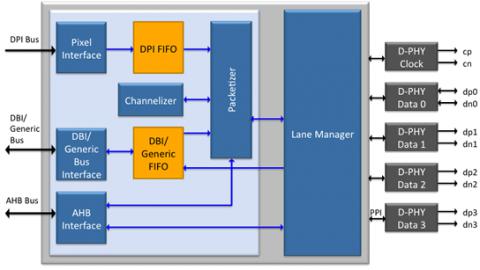

The Arasan DSI-2 Device Controller IP is designed to provide MIPI DSI-2 1.0 compliant high speed serial connectivity for mobile host processors using 1 to 4 D-PHYs depending on bandwidth needs. Serial connectivity to the display module’s DSI device is implemented using 1 to 4 D-PHY’s (also available from Arasan), depending on display bandwidth needs. This IP connects to the D-PHY’s through the PPI interface.

On the application processor side, Arasan’s DSI Host Controller provides the choice of DPI or DBI Interface to a graphics controller. A DBI interface provides downstream support of Types 1 to 3 display modules, and the DPI Interface is needed for Types 2 to 4 displays.

Initial configuration of this IP can be done through programmed IO over the AHB bus, however, other bus interfaces can be provided upon request.

On the application processor side, Arasan’s DSI Host Controller provides the choice of DPI or DBI Interface to a graphics controller. A DBI interface provides downstream support of Types 1 to 3 display modules, and the DPI Interface is needed for Types 2 to 4 displays.

Initial configuration of this IP can be done through programmed IO over the AHB bus, however, other bus interfaces can be provided upon request.

查看 MIPI DSI-2 Transmit Controller v1.0 详细介绍:

- 查看 MIPI DSI-2 Transmit Controller v1.0 完整数据手册

- 联系 MIPI DSI-2 Transmit Controller v1.0 供应商

Block Diagram of the MIPI DSI-2 Transmit Controller v1.0

DSI IP

- MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI DSI Receiver Controller v1.3

- MIPI DSI Transmit Controller v1.3

- MIPI D-PHY / C-PHY Combo IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI D-PHY Universal IP in TSMC 22ULP

- MIPI C-PHY/D-PHY Combo TX+ IP 4.5Gsps/4.5Gbps in TSMC N5