You are here:

MIPI D-PHY UMC 65LL

Arasan delivers you a MIPI D-PHY in the process node and lane configuration you need, conforming to your specific design constraints, with a complete GDSII that includes analog BIST and routing to your pads.

D-PHY is the physical layer specified for several of the key protocols within the MIPI® family of specifications.

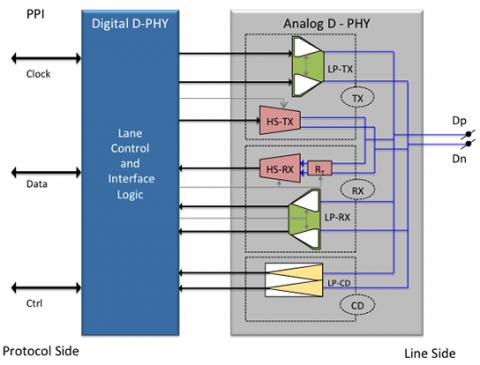

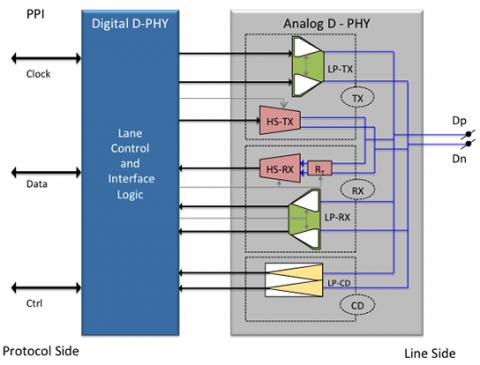

The Arasan’s MIPI D-PHY Analog Transceiver IP Core is fully compliant to the D-PHY specification version 1.1. It supports the MIPI® Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols. It is a universal PHY that can be configured as a transmitter, receiver or transceiver. The D-PHY consists of an analog front end to generate and receive the electrical level signals, and a digital back end to control the I/O functions.

The Arasan D-PHY provides a point to point connection between master and slave or host and device that comply with a relevant MIPI® standard. A typical configuration consists of a clock lane and 1-4 data lanes. The master/host is primarily the source of data and the slave/device is usually the sink of data. The D-PHY lanes can be configured for unidirectional or bidirectional lane operation, originating at the master and terminating at the slave. It can be configured to operate as a master or as a slave.

The D-PHY link supports a high speed (HS) mode for fast data traffic and a low power (LP) mode for control transactions. In HS mode, the low swing differential signal is able to support data transfers from 80 Mbps to 1.5 Gbps. In LP mode all wires operate as a single ended line capable of supporting 10 Mbps asynchronous data communications.

The Arasan D-PHY Analog Transceiver IP core implements the PPI interface recommended by the MIPI® working groups to easily interface to the required protocols.

D-PHY is the physical layer specified for several of the key protocols within the MIPI® family of specifications.

The Arasan’s MIPI D-PHY Analog Transceiver IP Core is fully compliant to the D-PHY specification version 1.1. It supports the MIPI® Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols. It is a universal PHY that can be configured as a transmitter, receiver or transceiver. The D-PHY consists of an analog front end to generate and receive the electrical level signals, and a digital back end to control the I/O functions.

The Arasan D-PHY provides a point to point connection between master and slave or host and device that comply with a relevant MIPI® standard. A typical configuration consists of a clock lane and 1-4 data lanes. The master/host is primarily the source of data and the slave/device is usually the sink of data. The D-PHY lanes can be configured for unidirectional or bidirectional lane operation, originating at the master and terminating at the slave. It can be configured to operate as a master or as a slave.

The D-PHY link supports a high speed (HS) mode for fast data traffic and a low power (LP) mode for control transactions. In HS mode, the low swing differential signal is able to support data transfers from 80 Mbps to 1.5 Gbps. In LP mode all wires operate as a single ended line capable of supporting 10 Mbps asynchronous data communications.

The Arasan D-PHY Analog Transceiver IP core implements the PPI interface recommended by the MIPI® working groups to easily interface to the required protocols.

查看 MIPI D-PHY UMC 65LL 详细介绍:

- 查看 MIPI D-PHY UMC 65LL 完整数据手册

- 联系 MIPI D-PHY UMC 65LL 供应商

Block Diagram of the MIPI D-PHY UMC 65LL

D-PHY 1.1 IP

- MIPI D-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI DSI-2 Receiver Controller v1.0

- MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI C-PHY-D-PHY Combo PHY IP on TSMC 28nm HPC+

- MIPI C-PHY V1.1 TSMC 28nm HPC+

- MIPI D-PHY Tx v1.1 ONLY @1.5ghz Ultra Low Power & Low Area for IoT & Wearables