You are here:

MIPI D-PHY/LVDS Combo CSI-2 RX (Receiver) in TSMC 28HPC+

The MXL-LVDS-DPHY-1p5G-CSI-2-RX-T-028HPC+ is a high-frequency low-power, low-cost, source-synchronous, Physical Layer supporting the MIPI Alliance Specification for D-PHY v2.1, which is backward compatible with MIPI Specification for D-PHY v1.2. The IP is configured as a MIPI Slave optimized for CSI-2 (Camera Serial Interface) applications. The High-Speed signals have a low voltage swing, while Low-Power signals have large swing. High-Speed functions are used for High-Speed data traffic while low power functions are mostly used for control.

The MXL-LVDS-DPHY-CSI2-RX is a high performance 4-channel LVDS Receiver implemented using digital CMOS technology. Both the serial and parallel data are organized into four channels. The parallel data can be 7 or 8 bits wide per channel. The input clock frequency is up to 75MHz or 85.7MHz. The Receiver is highly integrated and requires no external components. Great care was taken to ensure matching between the Data and Clock channels to maximize the receiver margin. The circuit is designed in a modular fashion and desensitized to process variations. This facilitates process migration, and results in a robust design.

The MXL-LVDS-DPHY-CSI2-RX is a high performance 4-channel LVDS Receiver implemented using digital CMOS technology. Both the serial and parallel data are organized into four channels. The parallel data can be 7 or 8 bits wide per channel. The input clock frequency is up to 75MHz or 85.7MHz. The Receiver is highly integrated and requires no external components. Great care was taken to ensure matching between the Data and Clock channels to maximize the receiver margin. The circuit is designed in a modular fashion and desensitized to process variations. This facilitates process migration, and results in a robust design.

查看 MIPI D-PHY/LVDS Combo CSI-2 RX (Receiver) in TSMC 28HPC+ 详细介绍:

- 查看 MIPI D-PHY/LVDS Combo CSI-2 RX (Receiver) in TSMC 28HPC+ 完整数据手册

- 联系 MIPI D-PHY/LVDS Combo CSI-2 RX (Receiver) in TSMC 28HPC+ 供应商

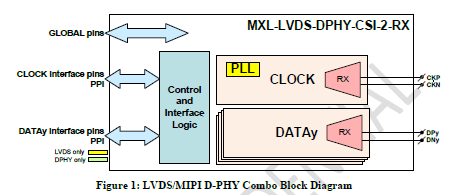

Block Diagram of the MIPI D-PHY/LVDS Combo CSI-2 RX (Receiver) in TSMC 28HPC+

d-phy IP

- MIPI D-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI DSI Receiver Controller v1.3

- MIPI DSI Transmit Controller v1.3

- MIPI CSI-2 controller Receiver v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI D-PHY / C-PHY Combo IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)