2-stage Power Amplifier 14.5GHz ultra-efficient Dual-Drive™ PA

MIPI D-PHY DSI RX (Receiver) in TSMC 40LP

The IP is configured as a MIPI slave optimized for display interface applications (DSI).

The High-Speed signals have a low voltage swing, while Low-Power signals have large swing. High-Speed functions are used for High-Speed Data traffic while low power functions are mostly used for control.

查看 MIPI D-PHY DSI RX (Receiver) in TSMC 40LP 详细介绍:

- 查看 MIPI D-PHY DSI RX (Receiver) in TSMC 40LP 完整数据手册

- 联系 MIPI D-PHY DSI RX (Receiver) in TSMC 40LP 供应商

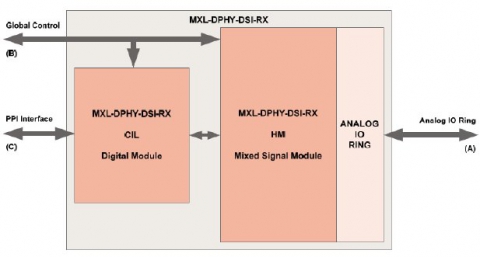

Block Diagram of the MIPI D-PHY DSI RX (Receiver) in TSMC 40LP

MIPI D-PHY Transmitter IP

- MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI D-PHY CSI-2 TX (Transmitter) in TSMC 28HPC+

- MIPI D-PHY CSI-2 TX+ (Transmitter) IP in TSMC 22ULL

- MIPI C-PHY/D-PHY Combo CSI-2 TX (Transmitter) in TSMC 40ULP

- MIPI D-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)