You are here:

MIPI D-PHY CSI-2 TX (Transmitter) in TSMC 65nm

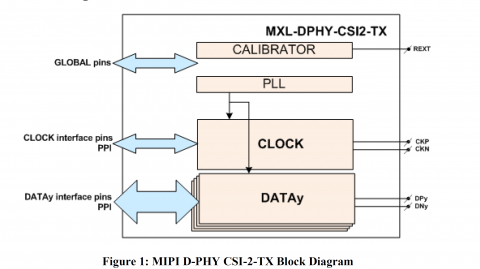

The MXL-DPHY-CSI-2-TX is a high-frequency low-power, low-cost, source synchronous, Physical Layer supporting the MIPI Alliance Specification for D-PHY v2.1, which is backward compatible with MIPI Specification for D-PHY v1.2. The IP is configured as a MIPI master optimized for CSI-2SM (Camera Serial Interface) applications.

The High-Speed signals have a low voltage swing, while Low-Power signals have large swing. High-Speed functions are used for high-Speed data traffic while low power functions are mostly used for control. The embedded PLL is highly integrated and requires no external components. The PLL incorporates a lock detector, one independent output divider and supports full power down modes. Differential circuit techniques are employed to attain low jitter in the noisy environment typical of multi-million gates digital chip. The circuit is designed in a modular fashion and desensitized to process variations.

The High-Speed signals have a low voltage swing, while Low-Power signals have large swing. High-Speed functions are used for high-Speed data traffic while low power functions are mostly used for control. The embedded PLL is highly integrated and requires no external components. The PLL incorporates a lock detector, one independent output divider and supports full power down modes. Differential circuit techniques are employed to attain low jitter in the noisy environment typical of multi-million gates digital chip. The circuit is designed in a modular fashion and desensitized to process variations.

查看 MIPI D-PHY CSI-2 TX (Transmitter) in TSMC 65nm 详细介绍:

- 查看 MIPI D-PHY CSI-2 TX (Transmitter) in TSMC 65nm 完整数据手册

- 联系 MIPI D-PHY CSI-2 TX (Transmitter) in TSMC 65nm 供应商