You are here:

MIPI CSI2 Transmit Controller

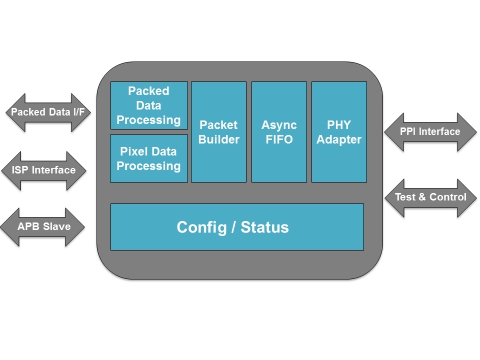

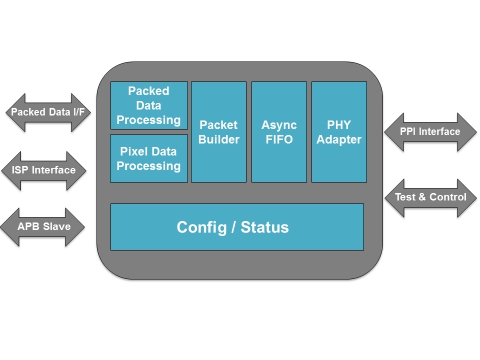

The MIPI CSI-2 Transmit Controller facilitates transmission over a standard high-speed unidirectional serial interface between CSI-2 Transmitter and Receiver. The receiver is typically a host image processor. The transmitter is typically part of a camera device supplying image data. The DPHY is the physical layer block to which the MIPI CSI-2 Transmit controller interfaces for transmission.

The CSI-2 Transmitter receives pixels by way of the ISP Interface or packed data by way of the PDI Interface. The CSI-2 Transmit Controller converts pixels into a byte stream, calculates and appends an ECC value to a short packet or to the header of a long packet. Packets are buffered in a FIFO and synchronized to the High-Speed Byte clock domain and sent to one or more of D-PHY lanes depending upon the lane distribution scheme set by the camera sensor.

The CSI-2 Transmitter receives pixels by way of the ISP Interface or packed data by way of the PDI Interface. The CSI-2 Transmit Controller converts pixels into a byte stream, calculates and appends an ECC value to a short packet or to the header of a long packet. Packets are buffered in a FIFO and synchronized to the High-Speed Byte clock domain and sent to one or more of D-PHY lanes depending upon the lane distribution scheme set by the camera sensor.

查看 MIPI CSI2 Transmit Controller 详细介绍:

- 查看 MIPI CSI2 Transmit Controller 完整数据手册

- 联系 MIPI CSI2 Transmit Controller 供应商

Block Diagram of the MIPI CSI2 Transmit Controller