Process Detector (For DVFS and monitoring process variation)

MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

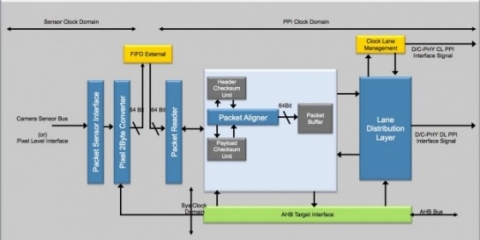

Pixel Data received from over the Camera Sensor Bus is packed into bytes by the Transmitter IP. The packing of the pixel into bytes follows the CSI-2 specification and based on the pixel format support. This IP calculates and appends an ECC/CRC value to a short packet (or) to the header of a long packet. Selection of ECC/CRC to the header is done based on the PHY connected. For the payload of a long packet carrying pixel data, this IP calculates its CRC value and appends to the packet as a Packet Footer (PF). The packet is buffered in a FIFO and sent to one or more D-PHY/C-PHY depending on the lane distribution scheme set by the camera sensor/user.

Arasan MIPI CSI-2 Transmitter is compliant to MIPI CSI-2 specification v2.1 and supports DPHY v2.1 and the MIPI C-PHY v1.2.

Arasan offers the C-PHY in a combination configuration that supports both C-PHY interfaces and D-PHY interfaces. Our implementation makes efficient use of the high frequency signally pins for a minimal overhead to support both physical interfaces.

查看 MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1. 详细介绍:

- 查看 MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1. 完整数据手册

- 联系 MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1. 供应商

Block Diagram of the MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

Video Demo of the MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

A Webinar on the MIPI CSI-2