You are here:

MIPI C-PHY/D-PHY Combo DSI RX (Receiver) IP in TSMC 28HPC+

The MXL-CPHY-DPHY-DSI-RX is a high-frequency low-power, low-cost, source-synchronous, physical Layer. The PHY is configured as MIPI Slave supporting camera interface CSI-2 v1.2 and display interface DSI v1.3 applications in the D-PHY mode. It also supports camera interface CSI-2 v1.3 and display interface DSI-C v1.0 applications in the C-PHY mode. The High-Speed signals have a low voltage swing, while Low-Power signals have large swing. High-Speed functions are used for High-Speed data traffic while low power functions are mostly used for control.

The C-PHY is based on 3-Phase symbol encoding technology delivering 2.28 bits per symbol over three-wire trios, operating with a symbol rate range of 80 to 2500 Msps per lane, which is the equivalent of about 182.8 to 5714 Mbps per lane.

The D-PHY supports a bit rate range of 80 to 1500 Mbps per Lane without deskew calibration and up to 2500 Mbps with deskew calibration.

The low-power mode and escape mode are the same in both the D-PHY and C-PHY modes. To minimize EMI, the drivers for low-power mode are slew-rate controlled and current limited. The maximum data rate in low-power mode is 10 Mbps. For a fixed clock frequency, the available data capacity of a PHY configuration can be increased by using more lanes. Effective data throughput can be reduced by employing burst mode communication.

The C-PHY is based on 3-Phase symbol encoding technology delivering 2.28 bits per symbol over three-wire trios, operating with a symbol rate range of 80 to 2500 Msps per lane, which is the equivalent of about 182.8 to 5714 Mbps per lane.

The D-PHY supports a bit rate range of 80 to 1500 Mbps per Lane without deskew calibration and up to 2500 Mbps with deskew calibration.

The low-power mode and escape mode are the same in both the D-PHY and C-PHY modes. To minimize EMI, the drivers for low-power mode are slew-rate controlled and current limited. The maximum data rate in low-power mode is 10 Mbps. For a fixed clock frequency, the available data capacity of a PHY configuration can be increased by using more lanes. Effective data throughput can be reduced by employing burst mode communication.

查看 MIPI C-PHY/D-PHY Combo DSI RX (Receiver) IP in TSMC 28HPC+ 详细介绍:

- 查看 MIPI C-PHY/D-PHY Combo DSI RX (Receiver) IP in TSMC 28HPC+ 完整数据手册

- 联系 MIPI C-PHY/D-PHY Combo DSI RX (Receiver) IP in TSMC 28HPC+ 供应商

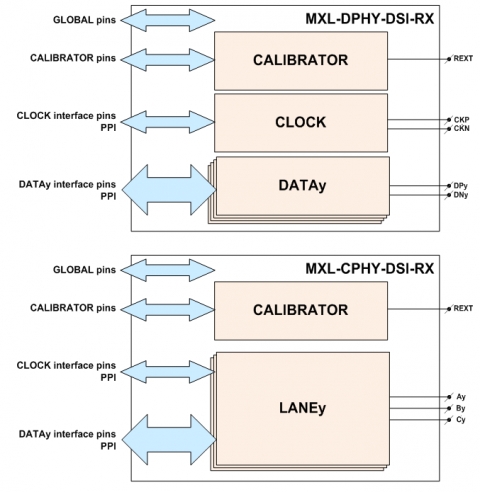

Block Diagram of the MIPI C-PHY/D-PHY Combo DSI RX (Receiver) IP in TSMC 28HPC+

MIPI D-PHY IP

- MIPI D-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI DSI Receiver Controller v1.3

- MIPI DSI Transmit Controller v1.3

- MIPI CSI-2 controller Receiver v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI D-PHY / C-PHY Combo IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)