You are here:

MIPI C/D-PHY 组合 Tx IP,在 TSMC 40 LP 中经过硅验证

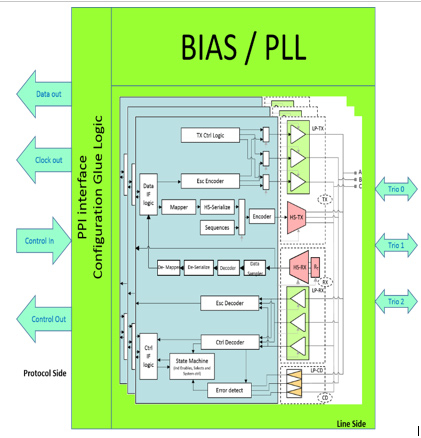

在产品生产中,工艺节点通常采用C-PHY/D-PHY Combo来实现低功耗配置和减少生产成本。客户可在D-PHY或C-PHY模式下配置这个Combo PHY IP以实现不同领域应用的适配化。这个IP还支持PPI接口,能够快捷地连接到CIS-2或DSI控制器。在各种铸造工艺中,D-PHY和C/D-PHY Combo 都配备了最具竞争力的PPA(性能、功率和面积)和标准兼容性。此外,这个Combo PHY IP嗨通过ISO 26262 ASIL-B认证的MIPI D-PHY规范,提供了大量有关汽车多媒体应用的功能。

查看 MIPI C/D-PHY 组合 Tx IP,在 TSMC 40 LP 中经过硅验证 详细介绍:

- 查看 MIPI C/D-PHY 组合 Tx IP,在 TSMC 40 LP 中经过硅验证 完整数据手册

- 联系 MIPI C/D-PHY 组合 Tx IP,在 TSMC 40 LP 中经过硅验证 供应商