MACsec Protocol Engine for 10/100/1000 Ethernet

Featuring a configurable number of Security Associations (up to 64k), this protocol engine supports multiple security channels and can implement multiple Security Entities (SecYs). It operates in full duplex mode, at line speed per direction for 1000/100/10 Mbps connections. It does so by implementing a 32-bit wide data path, which provides adequate performance while minimizing silicon resources.

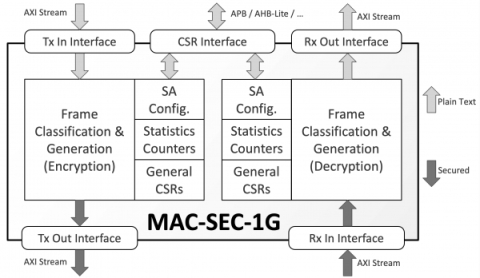

Designed for ease of integration, the MAC-SEC-1G core is a fully synchronous, single-clock domain design that uses standardized interfaces and can be optionally pre-integrated with companion cores available from CAST.

The control and status registers of the core are accessible via a generic 32-bit memory-mapped slave interface. Interface bridg-es delivered with the core can convert this generic host interface to a generic 8-bit memory-mapped interface or a 32-bit APB, AHB-Lite, Avalon-MM, or Wishbone interface. Packet data are input and output via AXI Stream interfaces with configurable data width, enabling direct connection to Ethernet MACs, PTP timestamping units, or other higher-layer protocol engines. Interface bridges and a DMA engine capable of driving the AXI Stream interfaces are available separately and can be used in cases where it is preferable to move data to and from the core over a memory-mapped bus. The core can be delivered pre-integrated with the Low-Latency Ethernet MAC or any of the Ethernet TSN cores available from CAST.

查看 MACsec Protocol Engine for 10/100/1000 Ethernet 详细介绍:

- 查看 MACsec Protocol Engine for 10/100/1000 Ethernet 完整数据手册

- 联系 MACsec Protocol Engine for 10/100/1000 Ethernet 供应商

Block Diagram of the MACsec Protocol Engine for 10/100/1000 Ethernet