TSMC GF Intel Low Phase Noise, High-performance Digital LC PLL

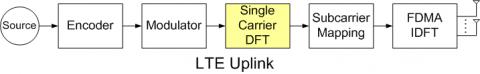

LTE Single Carrier FFT Circuit

A number of unique architectural characteristics allow this programmable circuit to provide simultaneously high throughput, high SNQR, low power, and minimal use of LUTs and registers in an FPGA fabric. Programmability is derived from a new type of memory-based array implementation that avoids addressing conflicts. The number of cycles per DFT is reduced as a result of a novel matrix oriented algorithmic approach. Clock speeds are high (~400MHz for 65nm technology) because all computations are "localized", leading to reduced interconnect delays that are less than the logic cell delays. Short critical path lengths also lower power dissipation. Minimal numbers of LUT/registers are needed because the adaptive floating-point scaling scheme keeps word lengths much shorter than traditional fixed-scaling and block-floating point schemes. Altogether these features result in extremely efficient implementations.

查看 LTE Single Carrier FFT Circuit 详细介绍:

- 查看 LTE Single Carrier FFT Circuit 完整数据手册

- 联系 LTE Single Carrier FFT Circuit 供应商

Block Diagram of the LTE Single Carrier FFT Circuit