You are here:

LRW-AES Core

Implementation of the older drafts standard IEEE P1619 required the NIST standard AES cipher in the LRW mode for encryption (AES-LRW). Note that the new drafts of the P1619 call for a different mode, XTS-AES (see our XTS cores). The LRW1 AES core is tuned for storage applications at the data rates of 3 Gbps and higher. The LRW2 family of cores covers a wide range of area / throughput combinations, allowing the designer to choose the smallest core that satisfies the desired clock/throughput requirements. All LRW cores contain the base AES core AES1 and are available for immediate licensing. LRW3 family is similar to LRW2, but supports 256-bit AES keys and no-penalty key and IV changes.

The design is fully synchronous and available in both source and netlist form.

The design is fully synchronous and available in both source and netlist form.

查看 LRW-AES Core 详细介绍:

- 查看 LRW-AES Core 完整数据手册

- 联系 LRW-AES Core 供应商

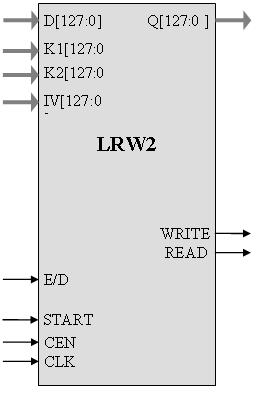

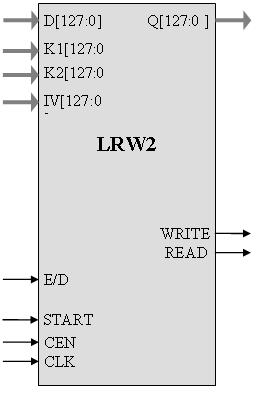

Block Diagram of the LRW-AES Core