Multi-Video-Source Multiplexing Serial Video Transmitter for MIPI CSI2

You are here:

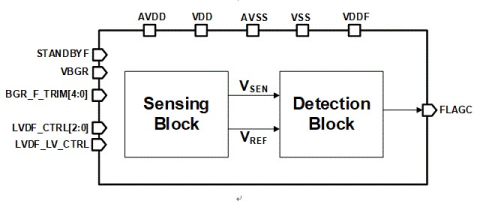

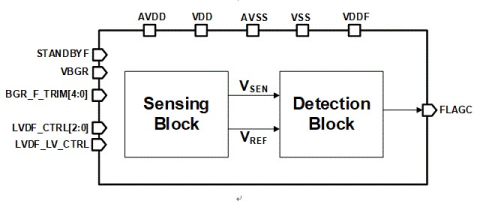

Low Voltage Detector

The low voltage detector is a supervisory circuit to monitor the logic power voltage and NAND power voltage. The low voltage detector flags when the monitored voltages are lower than each detection voltage level. The detection levels can be controlled by adjusting the input signals. It has one output, FLAGC. When the monitored voltages fall down through the detect voltage level, FLAGC will change from high to low. The detect level is 2.10V and 2.35V. There is no BGR embedded in this low voltage detector, reference voltage should be provided by outside.

查看 Low Voltage Detector 详细介绍:

- 查看 Low Voltage Detector 完整数据手册

- 联系 Low Voltage Detector 供应商

Block Diagram of the Low Voltage Detector