You are here:

Low Power PLL for 55nm UMC ULP CMOS

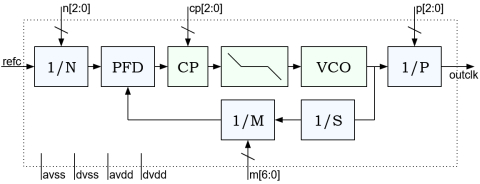

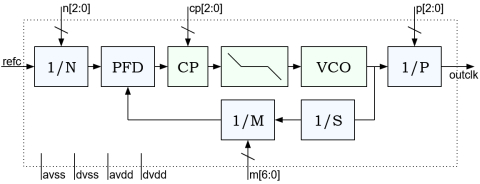

The OT3135 is a flexible low power clock multiplier PLL function with a wide range of input and output frequencies, and is designed for UMC 55nm, CMOS processes.

查看 Low Power PLL for 55nm UMC ULP CMOS 详细介绍:

- 查看 Low Power PLL for 55nm UMC ULP CMOS 完整数据手册

- 联系 Low Power PLL for 55nm UMC ULP CMOS 供应商

Block Diagram of the Low Power PLL for 55nm UMC ULP CMOS

clock IP

- TSMC CLN7FF 7nm Clock Generator PLL - 800MHz-4000MHz

- TSMC Samsung GF Intel CML mux - on-chip clock buffer

- TSMC FPD-Link / OpenLDI / LVDS forwarded clock SERDES Link

- Adaptive Clock Generation Module for DVFS and Droop Response

- TSMC CLN20SOC 20nm Clock Generator PLL - 700MHz-3500MHz

- MEMS-based Clock Generator with On-chip Temperature Compensation