You are here:

16位精简指令架构(RISC)处理器 – 带缓存的低成本 & 低功耗CPU

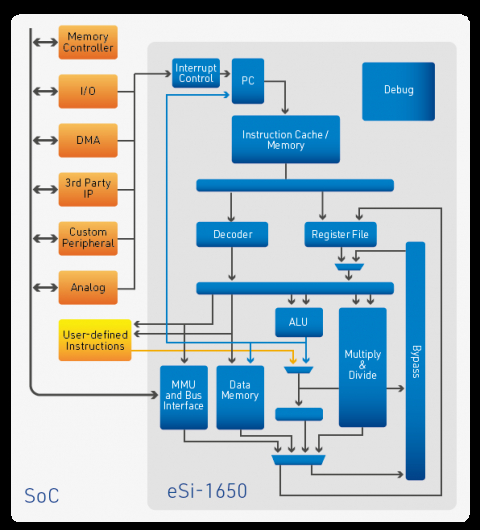

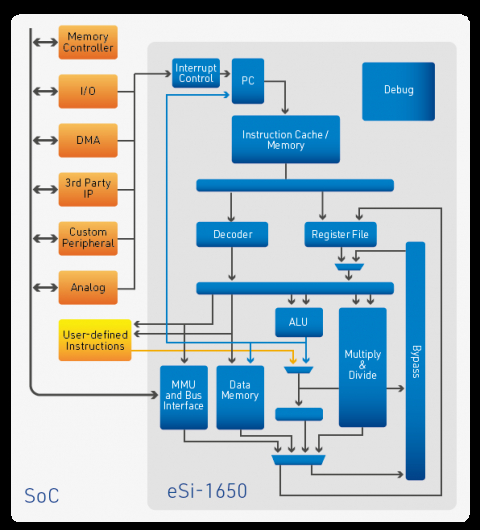

eSi-1650是一款带有指令缓存的16位CPU。它主要面向目前采用8位CPU的低功耗的应用场景,或者那些32位处理器在面积或功耗太大的场景。 通过集成指令缓存,在使用片上NVM核Flash作为程序内存的情况下,eSi-1650可以提供较高的性能,同时核心面积核功耗控制在较低的水平。

由于CPU主频主要受限于内存的速率,通过使用缓存,在成熟的制程下eSi-1650可以达到更高的主频。 使用缓存同时带来整体功耗的降低,因为读缓存比读Flash功耗低。 指令缓存可以小于一块完整的影子RAM(shadow RAM)。

由于采用了精简指令(RISC)流水线,虽然eSi-1650是16位处理器,它的逻辑门数量却跟8位处理器一样少。 在数据通路和寄存器都是16位的情况下,运行应用程序需要的时钟周期更少。 因此,可以通过CPU降频或者让CPU更快的进入省电模式来节省大量的能耗。

eSi-1650的指令集支持丰富的算数运算,比如32位整数乘除,累乘。 它同时提供一系列的应用场景可选指令和寻址模式。 支持位操作指令,比如位提取,位插入,clz,popcnt,ffs和位翻转等。 支持整数平方根,绝对值,min/max,crc和partiy指令。 Wait-for-interrupt指令允许快速的进入低功耗状态,支持对时钟频率和功耗进行限制。

对于那些需要极高的性能或者极低的功耗的场景,可以通过用户自定义指令和寄存器来支持实现。

同时支持用户态和核心态,特权指令和内存保护可以通过可选的MPU实现,操作系统可以跟应用程序有效隔离,从而得到充分的保护。

硬件调试支持硬件断点,观察点,跟踪,性能计数器,空指针探测,单步。这些特性可以有效的支撑对运行在ROM,FLASH和RAM上的程序进行快速调试。

由于CPU主频主要受限于内存的速率,通过使用缓存,在成熟的制程下eSi-1650可以达到更高的主频。 使用缓存同时带来整体功耗的降低,因为读缓存比读Flash功耗低。 指令缓存可以小于一块完整的影子RAM(shadow RAM)。

由于采用了精简指令(RISC)流水线,虽然eSi-1650是16位处理器,它的逻辑门数量却跟8位处理器一样少。 在数据通路和寄存器都是16位的情况下,运行应用程序需要的时钟周期更少。 因此,可以通过CPU降频或者让CPU更快的进入省电模式来节省大量的能耗。

eSi-1650的指令集支持丰富的算数运算,比如32位整数乘除,累乘。 它同时提供一系列的应用场景可选指令和寻址模式。 支持位操作指令,比如位提取,位插入,clz,popcnt,ffs和位翻转等。 支持整数平方根,绝对值,min/max,crc和partiy指令。 Wait-for-interrupt指令允许快速的进入低功耗状态,支持对时钟频率和功耗进行限制。

对于那些需要极高的性能或者极低的功耗的场景,可以通过用户自定义指令和寄存器来支持实现。

同时支持用户态和核心态,特权指令和内存保护可以通过可选的MPU实现,操作系统可以跟应用程序有效隔离,从而得到充分的保护。

硬件调试支持硬件断点,观察点,跟踪,性能计数器,空指针探测,单步。这些特性可以有效的支撑对运行在ROM,FLASH和RAM上的程序进行快速调试。

查看 16位精简指令架构(RISC)处理器 – 带缓存的低成本 & 低功耗CPU 详细介绍:

- 查看 16位精简指令架构(RISC)处理器 – 带缓存的低成本 & 低功耗CPU 完整数据手册

- 联系 16位精简指令架构(RISC)处理器 – 带缓存的低成本 & 低功耗CPU 供应商

Block Diagram of the 16位精简指令架构(RISC)处理器 – 带缓存的低成本 & 低功耗CPU

RISC IP

- DSP-enhanced ARC EMxD and HS4xD processors provide combined RISC + DSP processing for computation intensive applications

- Ultra low power, high-performance DSP / controller RISC core

- 32-bit High Performance Single/Multicore RISC Processor

- 32-bit High Performance Single/Multicore RISC System-on-Chip

- 32-bit High Performance Single/Multicore RISC Processor with code compression

- 32-bit High Performance Single/Multicore RISC System-on-Chip with code compression