You are here:

Low-Noise Bandgap Reference - Low Noise: 63nV/√Hz, PSRR: -80dB TSMC 0.18μm CMOS (CLM18)

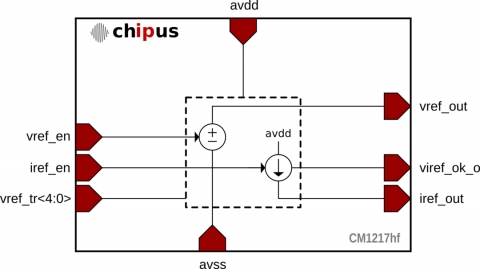

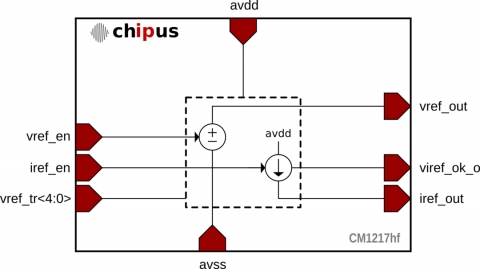

This macro-cell is a low noise, high PSRR voltage reference core designed for TSMC 0.18μm (CLM18) CMOS technology. The core is ideal for applications where noise performance is critical. The circuit generates a buffered 1.185V, temperature-compensated bandgap voltage reference (40ppm/◦C). A 5-bit trimming is available and guarantees ±1.5% output voltage accuracy. A 25μA reference current source (PTAT) for external use is also included.

查看 Low-Noise Bandgap Reference - Low Noise: 63nV/√Hz, PSRR: -80dB TSMC 0.18μm CMOS (CLM18) 详细介绍:

- 查看 Low-Noise Bandgap Reference - Low Noise: 63nV/√Hz, PSRR: -80dB TSMC 0.18μm CMOS (CLM18) 完整数据手册

- 联系 Low-Noise Bandgap Reference - Low Noise: 63nV/√Hz, PSRR: -80dB TSMC 0.18μm CMOS (CLM18) 供应商

Block Diagram of the Low-Noise Bandgap Reference - Low Noise: 63nV/√Hz, PSRR: -80dB TSMC 0.18μm CMOS (CLM18)