Secure-IC's Securyzr Crypto Coprocessor with integrated Post-Quantum Cryptography IPs

You are here:

Lossless MJPEG Encoder

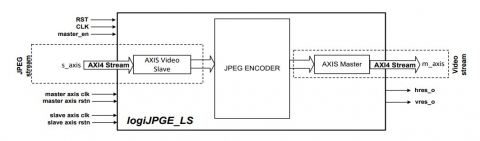

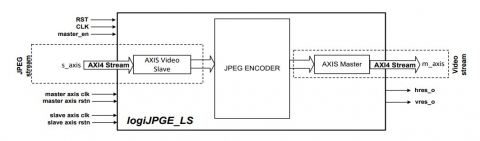

The logJPGE-LS Motion JPEG (MJPEG) Lossless Encoder is a Xylon's logicBRICKS IP Core for still image and video compression applications on AMD-Xilinx MPSoC, SoC and FPGA devices. It includes all logic blocks necessary for quick implementations of ARM AMBA AXI4 streaming-based FPGA/SoC architectures and enables on-the-fly JPEG compression of input video with resolutions up to 4096x16384 (including full HD video at 60FPS - 1080@60).

At the center of the logiJPGE-LS IP core is an encoder block, that works with the color component precision up to 12 bits and utilize standard JPEG headers on the output stream. The logiJPGE-LS IP Core supports compression of video input frames with one color component, the so-called color plane. A full multi-color video decompression requies division of JPEG encoded multi-color videos (i.e. Bayer, YUV, RGB) in separated JPEG LS frames per color component – color planes. One logiJPGE-LS IP core can sequentially compress all color planes to generate multi-color JPEG LS output. Alternatively, multiple logiJPGE-LS IP cores instantiated in a parallel can compress all input color planes at once.

In typical IP applications, a input video stream is encoded (compressed) MJPEG and transferred to the IP core's output. The compressed video can be further processed by the next block in the video pipeline, or with an additional Xilinx IP such as AXI Video DMA, directly stored to off-chip memory. The logiJPGE-LS IP Core works smoothly with Xylon's logjJPGD-LS Lossless MJPEG Decoder IP Core, as well as other lossless MPJEG Decoders compatible with the Annex H of the ISO/IEC 10918-1 JPEG Standard. Xylon also offers a pair of lossy MJPEG compression (logiJPGE) and decompression (logiJPGD) IP cores which give the user the ability to tune the level of compression used.

At the center of the logiJPGE-LS IP core is an encoder block, that works with the color component precision up to 12 bits and utilize standard JPEG headers on the output stream. The logiJPGE-LS IP Core supports compression of video input frames with one color component, the so-called color plane. A full multi-color video decompression requies division of JPEG encoded multi-color videos (i.e. Bayer, YUV, RGB) in separated JPEG LS frames per color component – color planes. One logiJPGE-LS IP core can sequentially compress all color planes to generate multi-color JPEG LS output. Alternatively, multiple logiJPGE-LS IP cores instantiated in a parallel can compress all input color planes at once.

In typical IP applications, a input video stream is encoded (compressed) MJPEG and transferred to the IP core's output. The compressed video can be further processed by the next block in the video pipeline, or with an additional Xilinx IP such as AXI Video DMA, directly stored to off-chip memory. The logiJPGE-LS IP Core works smoothly with Xylon's logjJPGD-LS Lossless MJPEG Decoder IP Core, as well as other lossless MPJEG Decoders compatible with the Annex H of the ISO/IEC 10918-1 JPEG Standard. Xylon also offers a pair of lossy MJPEG compression (logiJPGE) and decompression (logiJPGD) IP cores which give the user the ability to tune the level of compression used.

查看 Lossless MJPEG Encoder 详细介绍:

- 查看 Lossless MJPEG Encoder 完整数据手册

- 联系 Lossless MJPEG Encoder 供应商

Block Diagram of the Lossless MJPEG Encoder