You are here:

Linear Regulator, Low-noise optimized for sensitive application such as RF or PLL blocks

-

查看 Linear Regulator, Low-noise optimized for sensitive application such as RF or PLL blocks 详细介绍:

- 查看 Linear Regulator, Low-noise optimized for sensitive application such as RF or PLL blocks 完整数据手册

- 联系 Linear Regulator, Low-noise optimized for sensitive application such as RF or PLL blocks 供应商

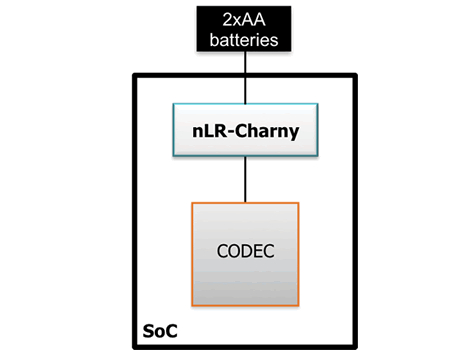

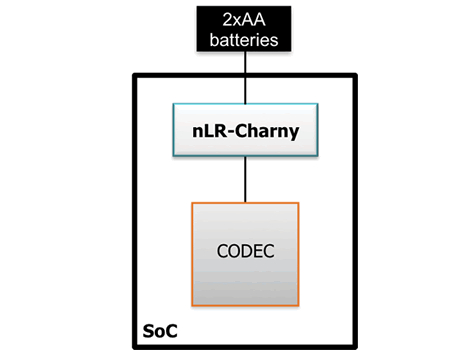

Block Diagram of the Linear Regulator, Low-noise optimized for sensitive application such as RF or PLL blocks