RT-120 Compact Root of Trust for IoT and IIoT, sensors and gateways

You are here:

Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks

nLR-Charny-ref-[1.62-3.63]-[0.8-2.5]-Ixx.02, as any Power Management Virtual Component designed by Dolphin Design, is readily retargetable toward any submicron CMOS process.

查看 Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks 详细介绍:

- 查看 Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks 完整数据手册

- 联系 Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks 供应商

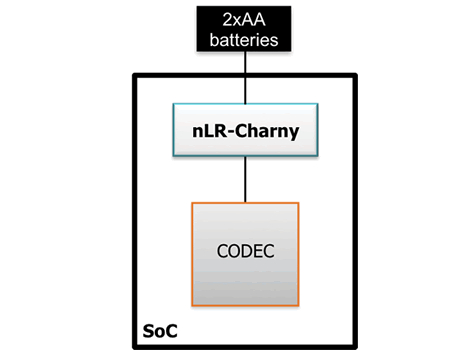

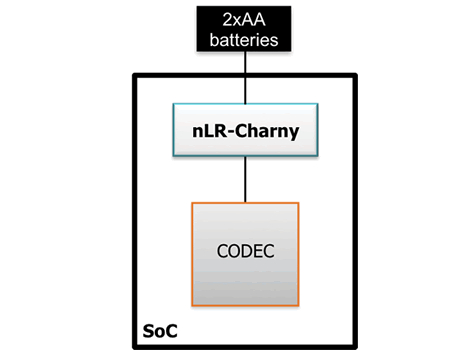

Block Diagram of the Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks