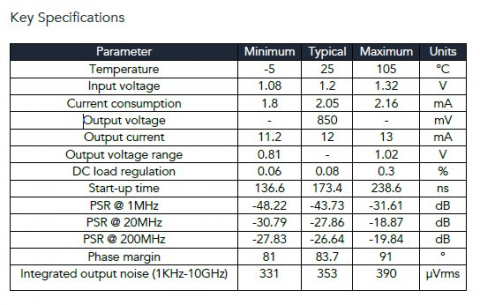

Linear Low-Dropout Regulator (Output Voltage 0.9V)

The regulator architecture provides high Power Supply Rejection (PSR) and low noise making it suitable for analog and RF applications.

查看 Linear Low-Dropout Regulator (Output Voltage 0.9V) 详细介绍:

- 查看 Linear Low-Dropout Regulator (Output Voltage 0.9V) 完整数据手册

- 联系 Linear Low-Dropout Regulator (Output Voltage 0.9V) 供应商

Block Diagram of the Linear Low-Dropout Regulator (Output Voltage 0.9V)

Bandgap Voltage Reference IP

- Bandgap Voltage Reference (0.6V and 0.8V References)

- Ultra-Low-Power Bandgap Voltage Reference in 40nm CMOS

- Ultra-Low-Power Bandgap Voltage Reference in 28nm CMOS

- Ultra-Low-Power Bandgap Voltage Reference in 6nm CMOS

- Ultra-Low-Power Bandgap Voltage Reference in 12nm CMOS

- Accurate BandGap Voltage/Current Reference Generator