You are here:

Linear LDO Low-Dropout Voltage Regulator Samsung

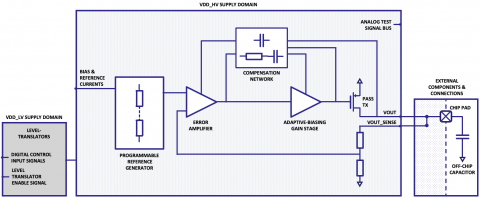

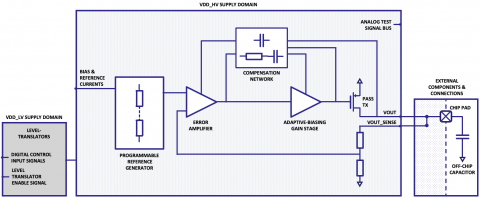

The agileLDO is a linear low-dropout voltage regulator (LDO) providing precision and programmable voltage regulation across a wide range of input and output voltages. The regulator architecture provides a high dynamic performance making it suitable for demanding digital applications. Whilst the low noise and high PSRR lends itself to powering noise-sensitive analog circuits.

查看 Linear LDO Low-Dropout Voltage Regulator Samsung 详细介绍:

- 查看 Linear LDO Low-Dropout Voltage Regulator Samsung 完整数据手册

- 联系 Linear LDO Low-Dropout Voltage Regulator Samsung 供应商

Block Diagram of the Linear LDO Low-Dropout Voltage Regulator Samsung

LDO IP

- LDO Voltage Regulator, 30 mA, Adjustable 0.45 V to 0.9 V Output

- LDO Voltage Regulator, 250 mA, Adjustable 0.45 V to 0.9 V Output

- Analog Front End: 2x 12-bit 4 GSPS IQ ADCs, 2x 12-bit 8GSPS IQ DACs, bandgap, temp sensor, PLL, 4 x LDO

- LDO Linear Voltage Regulator

- Ultra-low quiescent LDO voltage regulator in TSMC 22ULL

- Capless 1.8V output LDO with 2.0-3.6V input range - 0.18 EF