LIN 2.2、2.1 和 1.3 协议控制器 IP

查看 LIN 2.2、2.1 和 1.3 协议控制器 IP 详细介绍:

- 查看 LIN 2.2、2.1 和 1.3 协议控制器 IP 完整数据手册

- 联系 LIN 2.2、2.1 和 1.3 协议控制器 IP 供应商

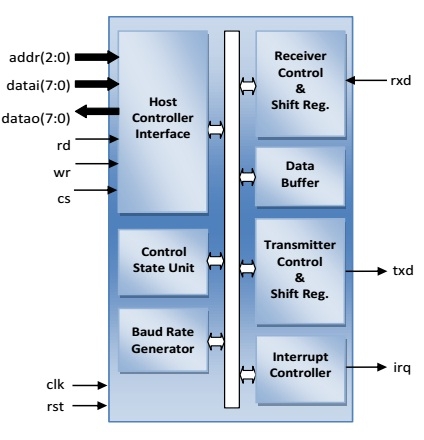

Block Diagram of the LIN 2.2、2.1 和 1.3 协议控制器 IP

LIN Bus IP IP

- LIN Bus Master/Slave Controller Core

- LIN Bus Controller – Basic and Safety-Enhanced

- Local Interconnect Network (LIN) Soft Controller IP

- Configurable UART with FIFO, software and hardware flow control

- High Speed UART IP core - Universal Aysynchronous Receiver / Transmitter

- 8-bit FAST Microcontrollers Family