LDO Voltage Regulator, 30 mA, Adjustable 0.45 V to 0.9 V Output

You are here:

Lightweight Configurable Display Controller

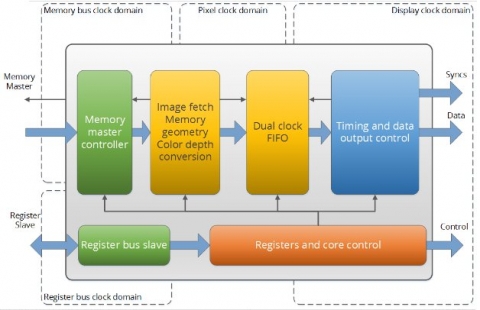

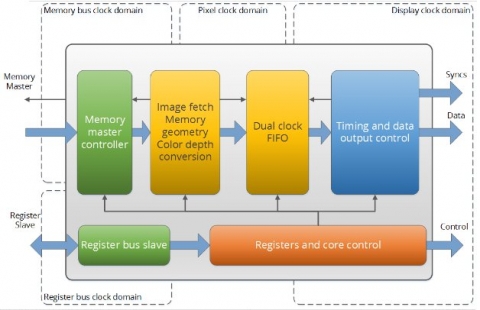

The IQ-DispLite is a lightweight, fully software configurable display controller IP core. It performs continuous refresh of graphical flat panel displays (TFT LCD, AMOLED) from a designated frame buffer located in a memory device mapped to the system bus. SDRAM and SRAM devices are supported as frame buffers, depending on the bandwidth requirements.

IQ-DispLite is designed to provide an optimum tradeoff of performance and resource utilization in FPGA devices while retaining a high degree of configurability. All display settings (timing parameters, resolution, color depth) can be configured by software at run-time.

The IP core can be additionally scaled down at compile time by reducing bus widths and fixing timing parameters, allowing the user to fully optimize the IQ-DispLite for a specific configuration.

The core has been rigorously tested in functional simulation and actual hardware. The core is accompanied with an automated testbench with a display simulation model and a memory simulation model. The memory model can be initialized with the desired bitmap through simple software provided with the model.

This core is marked as "AMPPSM Approved" and "SOPC Builder Ready".

The "AMPPSM Approved" mark indicates that this core meets Altera's sales standards and that this core has passed rigorous engineering testing.

The "SOPC Builder Ready" mark indicates that this core features plug-and-play integration with Altera's SOPC builder and the Nios® II processor over the Avalon® system interconnect.

IQ-DispLite is designed to provide an optimum tradeoff of performance and resource utilization in FPGA devices while retaining a high degree of configurability. All display settings (timing parameters, resolution, color depth) can be configured by software at run-time.

The IP core can be additionally scaled down at compile time by reducing bus widths and fixing timing parameters, allowing the user to fully optimize the IQ-DispLite for a specific configuration.

The core has been rigorously tested in functional simulation and actual hardware. The core is accompanied with an automated testbench with a display simulation model and a memory simulation model. The memory model can be initialized with the desired bitmap through simple software provided with the model.

This core is marked as "AMPPSM Approved" and "SOPC Builder Ready".

The "AMPPSM Approved" mark indicates that this core meets Altera's sales standards and that this core has passed rigorous engineering testing.

The "SOPC Builder Ready" mark indicates that this core features plug-and-play integration with Altera's SOPC builder and the Nios® II processor over the Avalon® system interconnect.

查看 Lightweight Configurable Display Controller 详细介绍:

- 查看 Lightweight Configurable Display Controller 完整数据手册

- 联系 Lightweight Configurable Display Controller 供应商

Block Diagram of the Lightweight Configurable Display Controller

lcd IP

- Display Controller - LCD / OLED Panels (AXI Bus)

- Display Controller - LCD / OLED Panels (AXI4 Bus)

- TFT/LCD/MIPI Display Controller and Composition Engine

- Display Controller - LCD / OLED Panels (AHB Bus)

- Display Controller - LCD / OLED Panels (AHB-Lite Bus)

- Display Controller - LCD 4K Digital Cinema (DCI)