MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

You are here:

- Silicon IP Catalog >

- Processor Solutions >

- Microcontroller >

- 8-Bit Microcontroller >

- 8051 Microcontroller

Legacy-Configurable 8051-Compatible Microcontroller

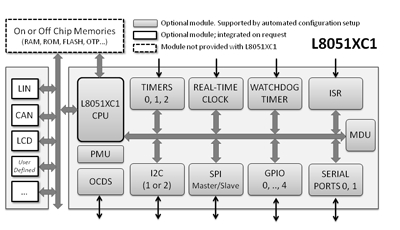

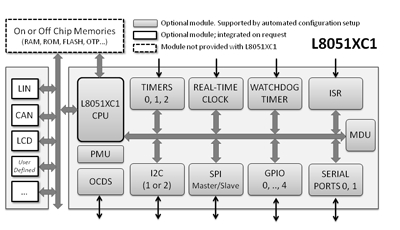

The L8051XC1 core implements an MCS®51-compatible microcontroller that is specially designed to match the timing and peripherals of legacy 8051 MCU based systems.

The core can be configured to execute an instruction every 12, 6, or 4 clock cycles. Architectural extensions are user-selectable, including multiple data-pointers, a multiply-division unit, and a power management unit. Furthermore, the 8051 CPU can be coupled with a wide range of peripherals matching the behavior and timing of peripherals found in legacy architectures from Intel, Phillips/NXP, Siemens/Infineon, Maxim/Dallas, Texas instruments and others. Several pre-configured versions are offered; custom variations are also available.

The L8051XC1 runs legacy code, but new software development is facilitated through CAST’s on-chip debugging option, and debug pods that cooperate with IAR Embedded Workbench & Keil uVision™ IDEs.

This new product builds on CAST’s experience with hundreds of 8051 IP customers going back to 1997. Designed for easy reuse in ASICs, structured ASICs, or FPGAs, the core is strictly synchronous, with positive-edge clocking (except in the optional debug & SPI modules), synchronous reset, and no internal tri-states. Representative 40nm ASIC results show the core to be conservative in its use of space, requiring just 7,000 to 40,000 gates.

The core can be configured to execute an instruction every 12, 6, or 4 clock cycles. Architectural extensions are user-selectable, including multiple data-pointers, a multiply-division unit, and a power management unit. Furthermore, the 8051 CPU can be coupled with a wide range of peripherals matching the behavior and timing of peripherals found in legacy architectures from Intel, Phillips/NXP, Siemens/Infineon, Maxim/Dallas, Texas instruments and others. Several pre-configured versions are offered; custom variations are also available.

The L8051XC1 runs legacy code, but new software development is facilitated through CAST’s on-chip debugging option, and debug pods that cooperate with IAR Embedded Workbench & Keil uVision™ IDEs.

This new product builds on CAST’s experience with hundreds of 8051 IP customers going back to 1997. Designed for easy reuse in ASICs, structured ASICs, or FPGAs, the core is strictly synchronous, with positive-edge clocking (except in the optional debug & SPI modules), synchronous reset, and no internal tri-states. Representative 40nm ASIC results show the core to be conservative in its use of space, requiring just 7,000 to 40,000 gates.

查看 Legacy-Configurable 8051-Compatible Microcontroller 详细介绍:

- 查看 Legacy-Configurable 8051-Compatible Microcontroller 完整数据手册

- 联系 Legacy-Configurable 8051-Compatible Microcontroller 供应商

Block Diagram of the Legacy-Configurable 8051-Compatible Microcontroller