LDPC Decoder for IS-GPS-800D Applications

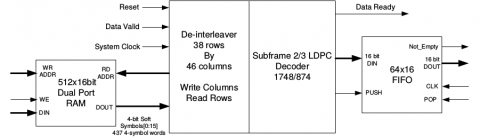

The VK3061 LDPC IP implements the error correction module in the GPS receiver, as well as the memories. It integrates the de-interleaver, subframe 2 LDPC decoder and subframe 3 LDPC decoder with both the DPRAM and the FIFO.

查看 LDPC Decoder for IS-GPS-800D Applications 详细介绍:

- 查看 LDPC Decoder for IS-GPS-800D Applications 完整数据手册

- 联系 LDPC Decoder for IS-GPS-800D Applications 供应商

Block Diagram of the LDPC Decoder for IS-GPS-800D Applications