MIPI C-PHY v2.0 D-PHY v2.1 RX 2 trios/2 Lanes in TSMC (N5, N3E, N3P)

You are here:

Jitter Cleaner PLL Digital Loop Filter

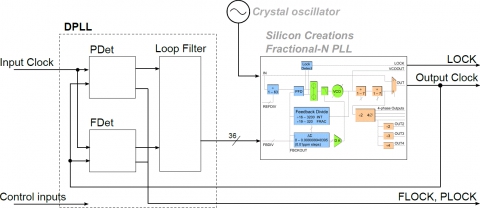

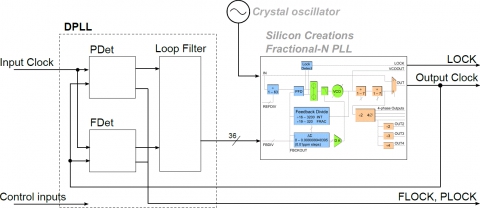

The DPLL is a digital loop filter/controller designed to be used in conjunction with Silicon Creations Fractional-N PLLs. The resulting dual-loop PLL can attenuate jitter in extremely noisy reference clocks (and "gapped clocks" such as in OTN SerDes repeater/switch systems) and multiply very low frequency clocks. The loop bandwidth of the combined PLL is determined by the digital loop filter and can be arbitrarily small while the quality of the output clock is determined by the connected Fractional-N PLL and its reference clock. The DPLL uses a modest number of gates and the resulting dual-loop PLL is fully integrated (no external components) with a total area little more than the embedded Fractional-N PLL.

查看 Jitter Cleaner PLL Digital Loop Filter 详细介绍:

- 查看 Jitter Cleaner PLL Digital Loop Filter 完整数据手册

- 联系 Jitter Cleaner PLL Digital Loop Filter 供应商

Block Diagram of the Jitter Cleaner PLL Digital Loop Filter