You are here:

JESD204B Tx-Rx PHY IP,在 TSMC 65GP/55GP 中经过硅验证

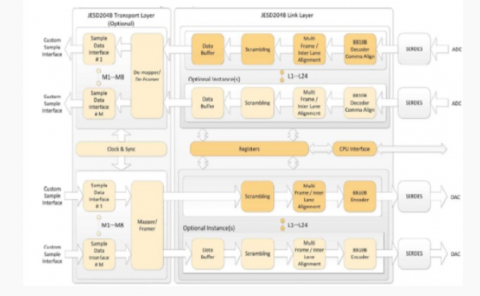

JESD204B控制器IP符合JEDEC JESD204B规范并针对任何ASIC、FPGA和ASSP技术进行了高度优化,这个设计对芯片的设置没有要求。这个解决方案默认提供每条车道高达12.5 Gbps的线速,同时保证数据对齐和同步。这个设计能够快速可靠地部署发射器(TX)和接收器(RX),并可选择紧密集成传输层选项,可动态配置以处理任何多转换器设备对准、多车道(MCDA-ML)的需求。这个IP核通过了硅验证,在UVM回归环境中进行了大量测试,并与主要的ADC/DAC供应商和领先的Serdes/PHY解决方案进行了互操作性测试。

查看 JESD204B Tx-Rx PHY IP,在 TSMC 65GP/55GP 中经过硅验证 详细介绍:

- 查看 JESD204B Tx-Rx PHY IP,在 TSMC 65GP/55GP 中经过硅验证 完整数据手册

- 联系 JESD204B Tx-Rx PHY IP,在 TSMC 65GP/55GP 中经过硅验证 供应商

Block Diagram of the JESD204B Tx-Rx PHY IP,在 TSMC 65GP/55GP 中经过硅验证

JESD204B Serdes PHY IP IP

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- Multi-protocol SerDes PMA in FDSOI (GF22FDX FDX 22FDX) - PCIe1 PCIe2 PCIe3 PCIe4 and more

- JESD204B Tx-Rx PHY IP, Silicon Proven in TSMC 28HPC+

- 32G Multi Rate SerDes PHY - GlobalFoundries 22FDX

- 32G Multi Rate Long Reach SerDes PHY - GlobalFoundries 12LP and 12LPP

- 32G Multi Rate Very Short Reach SerDes PHY - GlobalFoundries 12LP and 12LPP