You are here:

Internal Synchronous SRAM Controller Core

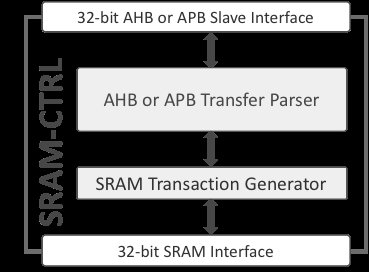

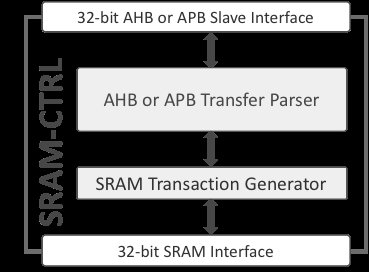

The SRAM-CTRL implements a SRAM Controller providing a standard AHB/APB interface to translate AHB/APB bus reads and writes into reads and writes with the signaling and timing of a standard 32-bit synchronous SRAM.

When the AHB interface is selected, the SRAM controller provides zero-wait-state AHB access to the synchronous SRAM in all cases except for the following back-to-back events: an AHB write directly followed by an AHB read. In this case, a single wait state is asserted.

When the APB interface is selected, the SRAM controller provides low latency APB access to the synchronous SRAM in all cases. APB write and read transfers are completed in two clock cycles.

The SRAM-CTRL core is rigorously verified, silicon-proven and available in RTL source or as a targeted FPGA netlist.

When the AHB interface is selected, the SRAM controller provides zero-wait-state AHB access to the synchronous SRAM in all cases except for the following back-to-back events: an AHB write directly followed by an AHB read. In this case, a single wait state is asserted.

When the APB interface is selected, the SRAM controller provides low latency APB access to the synchronous SRAM in all cases. APB write and read transfers are completed in two clock cycles.

The SRAM-CTRL core is rigorously verified, silicon-proven and available in RTL source or as a targeted FPGA netlist.

查看 Internal Synchronous SRAM Controller Core 详细介绍:

- 查看 Internal Synchronous SRAM Controller Core 完整数据手册

- 联系 Internal Synchronous SRAM Controller Core 供应商

Block Diagram of the Internal Synchronous SRAM Controller Core