You are here:

交织器/解交织

交织是通信系统中普遍使用的技术,以克服相关的信道噪声, 如突发错误或衰落。交织重新排列输入数据,使连续的数据间隔排列。在接收端,交织的数据经去交织器还原成原始序列。作为一个交织的结果,引入至传输通道的相关噪声在接收机中呈统计独立,从而可以更好的进行纠错。

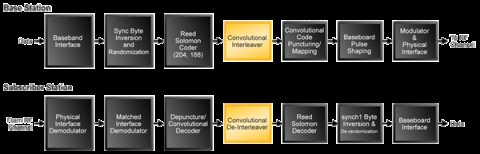

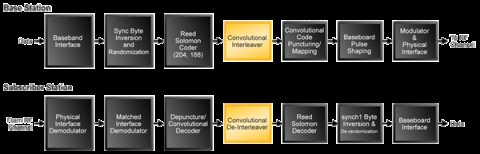

莱迪思的交织/去交织器IP核 支持矩形块类型和卷积架构。矩形交织在矩阵中逐行排列输入的数据。通过读取矩阵的列得到交织的数据。卷积交织将输入数据送入了多个分支,其中每个都有预定义长度的移位寄存器。从分支输出得到输出数据。莱迪思的卷积交织/去交织IP核符合ATSC和DVB标准,而矩形交织/去交织器符合IEEE 802.16a标准。

莱迪思的交织/去交织器IP核 支持矩形块类型和卷积架构。矩形交织在矩阵中逐行排列输入的数据。通过读取矩阵的列得到交织的数据。卷积交织将输入数据送入了多个分支,其中每个都有预定义长度的移位寄存器。从分支输出得到输出数据。莱迪思的卷积交织/去交织IP核符合ATSC和DVB标准,而矩形交织/去交织器符合IEEE 802.16a标准。

查看 交织器/解交织 详细介绍:

- 查看 交织器/解交织 完整数据手册

- 联系 交织器/解交织 供应商

Block Diagram of the 交织器/解交织

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software