You are here:

Interlaken-PHY

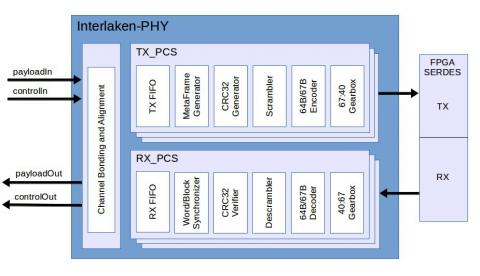

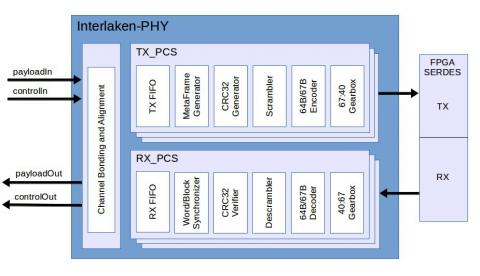

Interlaken is a royalty-free interconnect protocol that was developed by Cisco Systems and Cortina Systems in 2006. The full Interlaken protocol (described in the Interlaken Protocol Specification, v1.2) was designed to support chip-to-chip packet transfers in high-bandwidth networking equipment. A full Interlaken solution consists of the Interlaken Protocol Layer which runs on top of the Interlaken Framing Layer. The full Interlaken protocol is often viewed as too complex for designers who are looking for a lightweight, low-overhead way to connect multiple FPGAs, systems, or sensors. For these cases, the Interlaken Framing Layer gives us everything we need for an extremely scalable, high-bandwidth, low-overhead and lightweight FPGA interconnect that supports any FPGA device family all with a common user interface. The Interlaken Framing Layer is combined with the FPGA transceiver to form a complete IP core that we call the Interlaken-PHY IP Core.

查看 Interlaken-PHY 详细介绍:

- 查看 Interlaken-PHY 完整数据手册

- 联系 Interlaken-PHY 供应商

Block Diagram of the Interlaken-PHY

Interlaken IP

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- Multi-protocol SerDes PMA in FDSOI (GF22FDX FDX 22FDX) - PCIe1 PCIe2 PCIe3 PCIe4 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- Interlaken Controller

- Interlaken Controller

- Interlaken Communication Controller