You are here:

Interlaken Controller

Interlaken is a scalable chip-to-chip protocol, which ensures the integrity of reliable data transfer and managing data flows to prevent data overload. The Interlaken IP core is a highly optimized silicon and PHY agnostic implementation of the Interlaken Protocol version 1.2 targeting both ASICs and FPGAs. Our Interlaken controller supports up to 2.6 Tbps high-bandwidth performance and comes with an integrated Media Access layer.

The Interlaken Controller can be widely used in chip-to-chip transfers, it has an extensive feature-set available and allows scalability in number of logic channels (up to 2048), lanes (up to 48) and lane speed (up to 56 Gbps). The IP core is heavily tested in SystemVerilog random regression environment.

The Interlaken Controller can be widely used in chip-to-chip transfers, it has an extensive feature-set available and allows scalability in number of logic channels (up to 2048), lanes (up to 48) and lane speed (up to 56 Gbps). The IP core is heavily tested in SystemVerilog random regression environment.

查看 Interlaken Controller 详细介绍:

- 查看 Interlaken Controller 完整数据手册

- 联系 Interlaken Controller 供应商

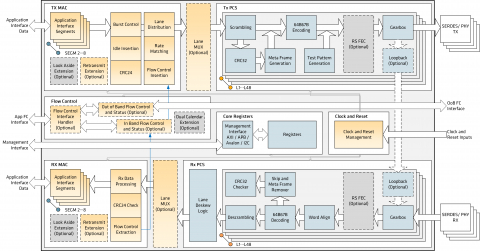

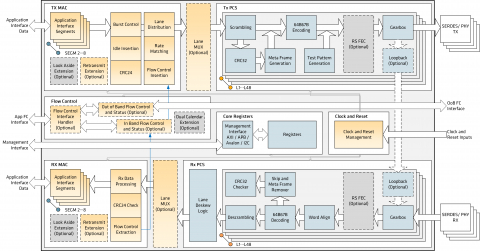

Block Diagram of the Interlaken Controller

Interlaken IP

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- Multi-protocol SerDes PMA in FDSOI (GF22FDX FDX 22FDX) - PCIe1 PCIe2 PCIe3 PCIe4 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- Interlaken Controller

- Interlaken Communication Controller

- Interlaken, 100G, 12 Lanes