You are here:

IEEE1588 & IEEE802.1AS PTP Hybrid Clock (HC) core

The PTP Hybrid Clock (HC) from NetTimeLogic is a combination of NetTimeLogic's PTP Transparent Clock (TC) and PTP Ordinary Clock (OC). It adds the Sync and Announce message processors to the design which allow synchronization of the clock according to IEEE1588 while keeping the timing aware frame forwarding feature of the TC. The OC will run in Slave or Master mode according to the configuration and Best-Master-Clock (BMC) algorithm. For resource optimization the OC can also be implemented as Slave-Only clock.

The HC is intercepting the path between an Ethernet PHY and an Ethernet core that forwards or handles Ethernet frames. Mostly this is used in daisy-chained networks. This allows message injection in parallel to data transfers from/to the Switching Core.

All datasets and algorithms are implemented completely in HW.

The HC is intercepting the path between an Ethernet PHY and an Ethernet core that forwards or handles Ethernet frames. Mostly this is used in daisy-chained networks. This allows message injection in parallel to data transfers from/to the Switching Core.

All datasets and algorithms are implemented completely in HW.

查看 IEEE1588 & IEEE802.1AS PTP Hybrid Clock (HC) core 详细介绍:

- 查看 IEEE1588 & IEEE802.1AS PTP Hybrid Clock (HC) core 完整数据手册

- 联系 IEEE1588 & IEEE802.1AS PTP Hybrid Clock (HC) core 供应商

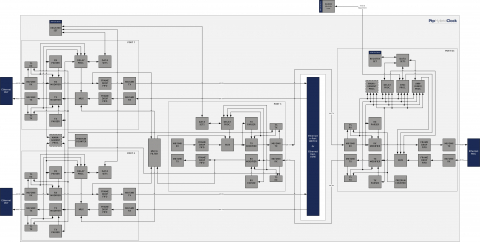

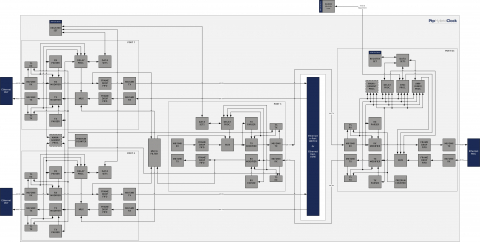

Block Diagram of the IEEE1588 & IEEE802.1AS PTP Hybrid Clock (HC) core

PTP IP

- 10 Gigabit Ethernet MAC with IEEE 1588 PTP Support and AVB for Auto

- IEEE1588 & IEEE802.1AS PTP Ordinary Clock (OC) core

- IEEE1588 & IEEE802.1AS PTP Transparent Clock (TC) core

- IEEE1588 & IEEE802.1AS PTP Timestamp Unit (TSU) core

- Gigabit Ethernet MAC with IEEE 1588 PTP Support and AVB for Auto

- Fast Ethernet 10/100 802.3 MAC with IEEE 1588 PTP Support