You are here:

IEEE 1588 Boundary, Slave And Master Clock

The IPC9004 utilizes IPClock’s state-of-the-art technology for IEEE 1588 v2 optimized for providing high quality frequency synchronization and Time of Day (ToD) over packet switched networks. Clock synchronization is required by many applications. For example, UMTS-FDD and Pseudo-wire (E1/T1) require the synchronization of frequency while LTE, WiMAX, CDMA2000 and GPS replacement require frequency synchronization, phase alignment and accurate Time of Day (ToD). The IPC9004 is IP core leveraging Xilinx® 7 series FPGAs. The IPC9004 is an application-agnostic, cost effective, reliable and standard compliant IEEE 1588 v2 BC and OC designed for enabling applications requiring high synchronization level. The IPC9004 is designed for easy field upgrades to support future enhancements as well as future clock synchronization standards.

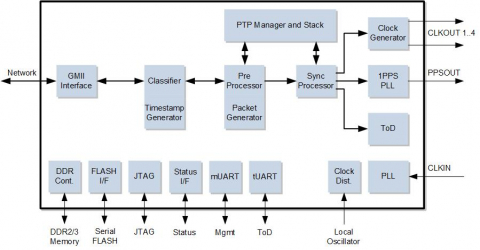

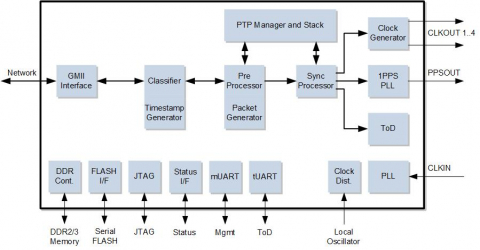

The IPC9004 can be set to operate as either IEEE 1588 v2 Boundary Clock or Ordinary Clock master or Ordinary Clock slave. The IEEE 1588 v2 protocol is a bidirectional protocol requiring all ports to transmit and receive 1588 v2 packets. Each packet received its time-stamp by the Timestamp Generator and classified by the Classifier. In the case the packet is 1588 v2 packet it is sent to the Pre-Processor along with its timestamp. The Pre-Processor is transferring the received general packets to the PTP Manager and Stack for further processing. In the case of 1588 v2 event packet the Pre-Processor compensate for part of the packet network impairments and prepare the data for the Sync Processor. The Sync Processor is comprised of a suite of algorithms that processes the data and controls the 1PPS PLL, the programmable clock output of the Clock Generator, and the ToD. The ToD is communicating with the ToD UART utilizing the NMEA protocol for either providing or getting the ToD from a GPS. The 1588 v2 packets are transmitted by the Packet Generator which is controlled by the PTP Manager and Stack. Each packet transmitted is time-stamped by the Timestamp Generator and this timestamp is either embedded into the packet or sent to the Pre-Processor depending on the packet type and selected mode of operation.

The IPC9004 can be set to operate as either IEEE 1588 v2 Boundary Clock or Ordinary Clock master or Ordinary Clock slave. The IEEE 1588 v2 protocol is a bidirectional protocol requiring all ports to transmit and receive 1588 v2 packets. Each packet received its time-stamp by the Timestamp Generator and classified by the Classifier. In the case the packet is 1588 v2 packet it is sent to the Pre-Processor along with its timestamp. The Pre-Processor is transferring the received general packets to the PTP Manager and Stack for further processing. In the case of 1588 v2 event packet the Pre-Processor compensate for part of the packet network impairments and prepare the data for the Sync Processor. The Sync Processor is comprised of a suite of algorithms that processes the data and controls the 1PPS PLL, the programmable clock output of the Clock Generator, and the ToD. The ToD is communicating with the ToD UART utilizing the NMEA protocol for either providing or getting the ToD from a GPS. The 1588 v2 packets are transmitted by the Packet Generator which is controlled by the PTP Manager and Stack. Each packet transmitted is time-stamped by the Timestamp Generator and this timestamp is either embedded into the packet or sent to the Pre-Processor depending on the packet type and selected mode of operation.

查看 IEEE 1588 Boundary, Slave And Master Clock 详细介绍:

- 查看 IEEE 1588 Boundary, Slave And Master Clock 完整数据手册

- 联系 IEEE 1588 Boundary, Slave And Master Clock 供应商

Block Diagram of the IEEE 1588 Boundary, Slave And Master Clock

IEEE1588 IP

- Multi Protocol Switch IP Core for Safe and Secure Ethernet Network

- Multi Protocol IO Concentrator (RDC) IP Core for Safe and Secure Ethernet Network

- Multi Protocol Switch IP Core for Safe and Secure Ethernet Network

- Multi Protocol Endpoint IP Core for Safe and Secure Ethernet Network

- Time Sensitive Networking (TSN) Single Port End Node core

- Time Sensitive Networking (TSN) Switched End Node core