You are here:

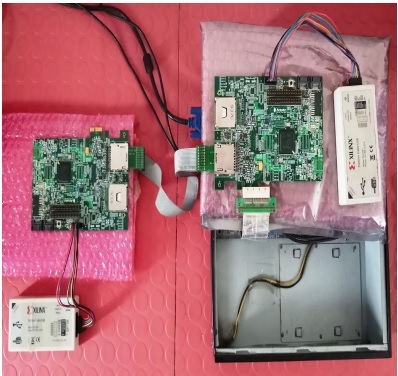

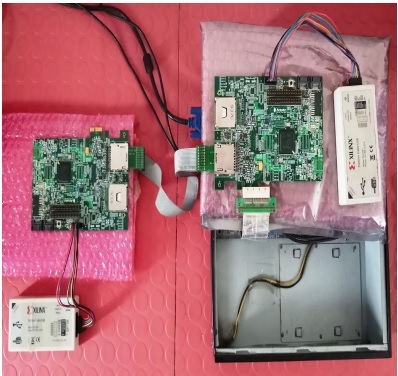

I3C Prototyping Kit (HDK) Total IP in a Box

The I3C Total IP in a box HDK gives I3C SoC developers all the resources they need to implement MIPI I3C specifications right out of the box. The HDK contains I3C Master and Slave FPGA Boards programmed with Arasan’s I3C Master & Slave IP respectively, I3C software stacks and reference schematics. The HDK will also be compatible with open source I3C drivers. Arasan’s I3C IP Cores are fully configurable across multiple parameters through simple scripts making it suitable for a variety of Sensor applications. Arasan’s I3C IP has been validated at the RTL with multiple I3C VIP vendors and the System Level at MIPI Interoperability Sessions with participation from the major companies actively implementing the I3C specifications. This ensures Arasan’s I3C IP is interoperable with multiple vendor solutions and is compliant to the specifications.

查看 I3C Prototyping Kit (HDK) Total IP in a Box 详细介绍:

- 查看 I3C Prototyping Kit (HDK) Total IP in a Box 完整数据手册

- 联系 I3C Prototyping Kit (HDK) Total IP in a Box 供应商

Block Diagram of the I3C Prototyping Kit (HDK) Total IP in a Box