You are here:

I2C & SMBus Controller

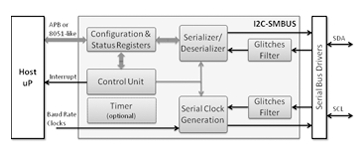

The I2C & SMBus Controller Core implements a serial interface controller for the Inter-Integrated Circuit (I2C) bus and the System Management Bus (SMBus).

The I2C & SMBus Controller Core can be programmed to operate either as a bus master or a slave, and it is easy to program and integrate. An arbitration mechanism allows operation in a multiple master bus and the SMBus provisioned clock synchronization mechanism allows fast-master/slow-slave communication. Furthermore, the core detects timeout and errors to prevent bus deadlocks, and can filter out glitches on the serial line. The control, status, and data registers of the I2C-SMBUS core are accessible via an AMBA APB or a generic memory mapped interface.

The I2C & SMBus Controller Core is a microcode-free design developed for reuse in ASIC and FPGA implementations. The design uses rising-edge-triggered flip-flops only with the reset type (i.e. asynchronous and/or synchronous) being configurable at synthesis time. Furthermore, the core does not use tri-states; therefore scan insertion is straightforward.

The I2C & SMBus Controller Core can be programmed to operate either as a bus master or a slave, and it is easy to program and integrate. An arbitration mechanism allows operation in a multiple master bus and the SMBus provisioned clock synchronization mechanism allows fast-master/slow-slave communication. Furthermore, the core detects timeout and errors to prevent bus deadlocks, and can filter out glitches on the serial line. The control, status, and data registers of the I2C-SMBUS core are accessible via an AMBA APB or a generic memory mapped interface.

The I2C & SMBus Controller Core is a microcode-free design developed for reuse in ASIC and FPGA implementations. The design uses rising-edge-triggered flip-flops only with the reset type (i.e. asynchronous and/or synchronous) being configurable at synthesis time. Furthermore, the core does not use tri-states; therefore scan insertion is straightforward.

查看 I2C & SMBus Controller 详细介绍:

- 查看 I2C & SMBus Controller 完整数据手册

- 联系 I2C & SMBus Controller 供应商

Block Diagram of the I2C & SMBus Controller