I2C Slave Controller with User Register Array / Memory / FIFO / AMBA Interface

查看 I2C Slave Controller with User Register Array / Memory / FIFO / AMBA Interface 详细介绍:

- 查看 I2C Slave Controller with User Register Array / Memory / FIFO / AMBA Interface 完整数据手册

- 联系 I2C Slave Controller with User Register Array / Memory / FIFO / AMBA Interface 供应商

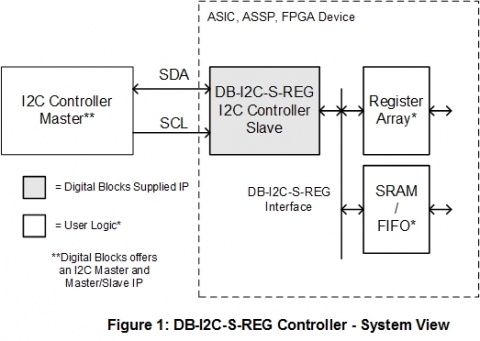

Block Diagram of the I2C Slave Controller with User Register Array / Memory / FIFO / AMBA Interface

I2C Slave Controller IP

- I2C and SPI Master/Slave Controller

- I2C Master/Slave Controller Core IP

- I2C Master / Slave Controller w/FIFO (AHB & AHB-Lite Bus)

- I2C Master / Slave Controller w/FIFO (APB Bus)

- Hs-Mode I2C Controller - 3.4 Mbps, Master / Slave w/FIFO

- I2C Slave Controller - Low Power, Low Noise Config of User Registers