I2C Slave Controller w/FIFO (APB Bus)

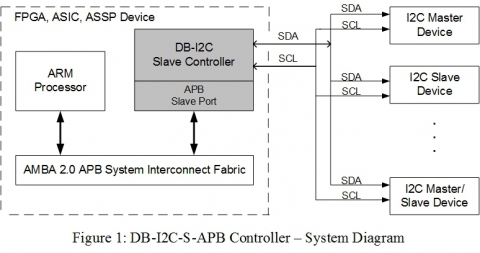

The DB-I2C-S-APB is a Slave I2C Controller that controls the Transmit or Receive of data to or from external Master I2C devices. Figure 1 depicts the system view of the DB-I2C-S-APB Controller IP Core embedded within an integrated circuit device.

查看 I2C Slave Controller w/FIFO (APB Bus) 详细介绍:

- 查看 I2C Slave Controller w/FIFO (APB Bus) 完整数据手册

- 联系 I2C Slave Controller w/FIFO (APB Bus) 供应商

Block Diagram of the I2C Slave Controller w/FIFO (APB Bus)

I2C Slave Controller IP

- I2C and SPI Master/Slave Controller

- I2C Master/Slave Controller Core IP

- I2C Master / Slave Controller w/FIFO (AHB & AHB-Lite Bus)

- I2C Master / Slave Controller w/FIFO (APB Bus)

- Hs-Mode I2C Controller - 3.4 Mbps, Master / Slave w/FIFO

- I2C Slave Controller - Low Power, Low Noise Config of User Registers