You are here:

I2C Slave Controller - Low Power, Low Noise Config with APB Interface

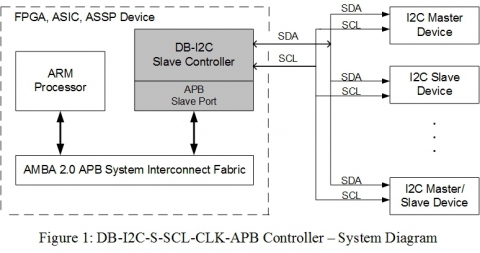

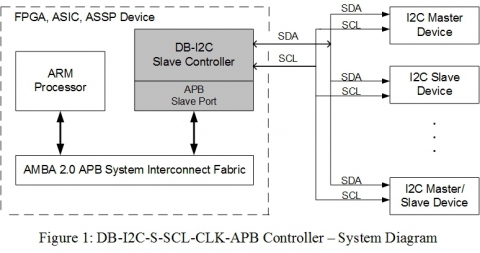

The Digital Blocks DB-I2C-S-SCL-CLK-APB Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high performance microprocessor via the AMBA 2.0 APB System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

The DB-I2C-S-SCL-CLK-APB, in the I2C Slave Controller Core managing the I2C protocol & physical layer, contains no free running clock, while interfacing through dual-clock FIFOs to the AMBA APB Bus, for a low power, low noise Microprocessor interface to the I2C Bus. The I2C Slave Controller Core runs off the external SCL clock while the APB side off the APB Clock.

The DB-I2C-S-SCL-CLK is a member of Digital Blocks DB-I2C Controller IP Core family, which includes I2C Master/Slave, I2C Master-only, and I2C Slave-only configurations.

The DB-I2C-S-SCL-CLK-APB, in the I2C Slave Controller Core managing the I2C protocol & physical layer, contains no free running clock, while interfacing through dual-clock FIFOs to the AMBA APB Bus, for a low power, low noise Microprocessor interface to the I2C Bus. The I2C Slave Controller Core runs off the external SCL clock while the APB side off the APB Clock.

The DB-I2C-S-SCL-CLK is a member of Digital Blocks DB-I2C Controller IP Core family, which includes I2C Master/Slave, I2C Master-only, and I2C Slave-only configurations.

查看 I2C Slave Controller - Low Power, Low Noise Config with APB Interface 详细介绍:

- 查看 I2C Slave Controller - Low Power, Low Noise Config with APB Interface 完整数据手册

- 联系 I2C Slave Controller - Low Power, Low Noise Config with APB Interface 供应商

Block Diagram of the I2C Slave Controller - Low Power, Low Noise Config with APB Interface

I2C Slave Controller IP

- I2C and SPI Master/Slave Controller

- I2C Master/Slave Controller Core IP

- I2C Master / Slave Controller w/FIFO (AHB & AHB-Lite Bus)

- I2C Master / Slave Controller w/FIFO (APB Bus)

- Hs-Mode I2C Controller - 3.4 Mbps, Master / Slave w/FIFO

- I2C Slave Controller - Low Power, Low Noise Config of User Registers