High Capacity Post-Quantum Cryptography Processor (PQF-HW-LAT)

You are here:

I2C Bus Master Controller Core

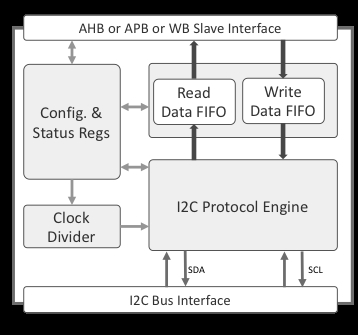

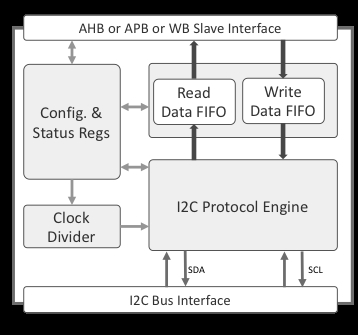

The I2C-MS core is a controller for the Inter-Integrated Circuit (I2C) bus. The highly configurable core can implement an I2C bus master, slave, or a combined master and slave, and it communicates with the host via an APB, AHB, or Wishbone slave interface.

The core supports all variations and configurations of I2C networks. It can be used in single- or multiple-master networks, running in any of bus standard-defined speeds, employing either 7-bit or 10-bit I2C slave addressing. Supporting clock stretching, it allows communication between slow slave and fast master.

Designed for ease of use and operation, the core allows choosing between. master and slave operation, and setting up I2C transfers at runtime with few register accesses. The core reports its internal status and the I2C bus status via its registers but also with via a rich set of interrupts.

The core supports all variations and configurations of I2C networks. It can be used in single- or multiple-master networks, running in any of bus standard-defined speeds, employing either 7-bit or 10-bit I2C slave addressing. Supporting clock stretching, it allows communication between slow slave and fast master.

Designed for ease of use and operation, the core allows choosing between. master and slave operation, and setting up I2C transfers at runtime with few register accesses. The core reports its internal status and the I2C bus status via its registers but also with via a rich set of interrupts.

The I2C-MS core is rigorously verified, and silicon-proven. It is available in synthesizable RTL and FPGA netlist forms, and includes everything required for successful implementation, including a sophisticated self-checking testbench, simulation scripts, test vectors, and expected results, synthesis scripts and comprehensive user documentation.

The core supports all variations and configurations of I2C networks. It can be used in single- or multiple-master networks, running in any of bus standard-defined speeds, employing either 7-bit or 10-bit I2C slave addressing. Supporting clock stretching, it allows communication between slow slave and fast master.

Designed for ease of use and operation, the core allows choosing between. master and slave operation, and setting up I2C transfers at runtime with few register accesses. The core reports its internal status and the I2C bus status via its registers but also with via a rich set of interrupts.

The core supports all variations and configurations of I2C networks. It can be used in single- or multiple-master networks, running in any of bus standard-defined speeds, employing either 7-bit or 10-bit I2C slave addressing. Supporting clock stretching, it allows communication between slow slave and fast master.

Designed for ease of use and operation, the core allows choosing between. master and slave operation, and setting up I2C transfers at runtime with few register accesses. The core reports its internal status and the I2C bus status via its registers but also with via a rich set of interrupts.

The I2C-MS core is rigorously verified, and silicon-proven. It is available in synthesizable RTL and FPGA netlist forms, and includes everything required for successful implementation, including a sophisticated self-checking testbench, simulation scripts, test vectors, and expected results, synthesis scripts and comprehensive user documentation.

查看 I2C Bus Master Controller Core 详细介绍:

- 查看 I2C Bus Master Controller Core 完整数据手册

- 联系 I2C Bus Master Controller Core 供应商

Block Diagram of the I2C Bus Master Controller Core