You are here:

I2C Bus Interface

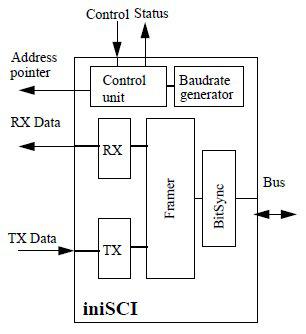

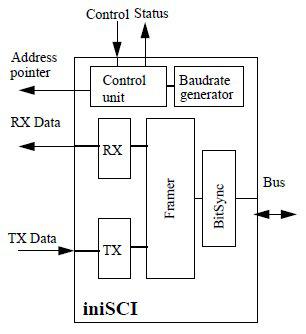

The serial controller interface (Single Master) core uses a two-wire bus for communicating between integrated circuits or standard peripherals like smart LCDs and keypads. The core contains the entire physical and data link layers, allowing it to handle bus timing and

frame generation/extraction, and thus reducing overhead from the system application. A flexible parallel interface is used for on-chip data transfer, facilitating integration of the iniSCI core to the rest of the system.

frame generation/extraction, and thus reducing overhead from the system application. A flexible parallel interface is used for on-chip data transfer, facilitating integration of the iniSCI core to the rest of the system.

查看 I2C Bus Interface 详细介绍:

- 查看 I2C Bus Interface 完整数据手册

- 联系 I2C Bus Interface 供应商

Block Diagram of the I2C Bus Interface