High Throughput Rate OFDM Baseband PHY Processor

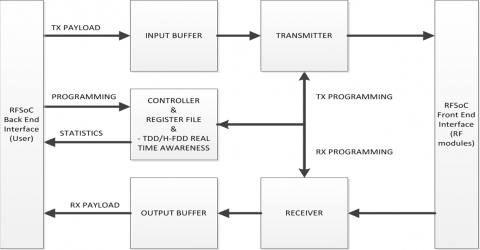

The Transmitter includes the Bit Level Processing Block (BLPB) and the Symbol Level Processing Block (SLPB). The BLPB operates on Users/Bursts payload bytes and uses Scrambling, FEC encoding, Interleaving and Symbol Modulation to produce I/Q modulated symbols. The SLPB operates on the produced symbols and uses them to generate the OFMDA-Symbol stream, inserts pilots and guard intervals, transforms the signal to the time domain (FFT transform) and adds the Cyclic Prefix.

The Receiver includes the Synchronizer, the SLPB and the BLPB main processing blocks. The Synchronizer searches for a known pattern (Preamble) in an effort to detect the exact start of a new incoming frame. It applies STO and CFO corrections on the signal. The SLPB operates on the synchronized signal and tries to compensate the channel impairments applied on the signal, while bringing it back to the frequency domain. It also demodulates the OFMDA symbols back to data symbols and provides them to the BLPB. The BLPB RX implements the exact op-posite procedure to the BLPB TX and recovers the corrected Users/Bursts payload bytes.

A real-time demonstration video of ntOFDM_HS_BBP IP Core can be downloaded from

http://www.noesis-tech.com/downloads/OFDM_Demo.mp4

查看 High Throughput Rate OFDM Baseband PHY Processor 详细介绍:

- 查看 High Throughput Rate OFDM Baseband PHY Processor 完整数据手册

- 联系 High Throughput Rate OFDM Baseband PHY Processor 供应商

Block Diagram of the High Throughput Rate OFDM Baseband PHY Processor