You are here:

High-Speed, Wide-Range Digital PLL in TSMC 40LP

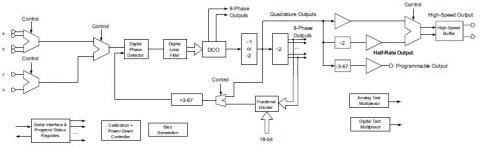

Granite Semicom has just shipped GDS-II of its totally-integrated (no off-chip components) Clock-Driver and Clock-Multiplying-Unit IP block including fractional-N in TSMC’s 40LP process; silicon is expected Q2 2013. In addition to porting its TSMC 40G version, a number of minor changes were incorporated. The oscillator was improved to have higher speed and less jitter, for a given power. Some critical current sources were modified to give an expected 40% reduction in long-term accumulated jitter. In addition, some feedback dividers where changed to give lower power. This block is intended for applications such as the CMU in a SERDES PHY, and for clock-driver applications. This IP block is a digital phased-lock-loop, plus an integrated voltage and current reference, a variety of input amplifiers (single-ended and differential, dc and ac-coupled), a number of programmable dividers, a serial interface for programming, and a high-speed 50 ohm driver capable of driving off-chip at full-speed. The specification is for the Digital PLL (DPLL_40LP) to operate between 0.5GHz and 7.5GHz over process corners between -40 and +125 degrees celsius; the power dissipation is less than 30 mw (for a 5GHz output), and the IP requires a 0.11 mm^2 area (not including pads and the output driver). Long term accumulated jitter is specified at less than 1ps rms accumulated over 260 periods.

查看 High-Speed, Wide-Range Digital PLL in TSMC 40LP 详细介绍:

- 查看 High-Speed, Wide-Range Digital PLL in TSMC 40LP 完整数据手册

- 联系 High-Speed, Wide-Range Digital PLL in TSMC 40LP 供应商

Block Diagram of the High-Speed, Wide-Range Digital PLL in TSMC 40LP

PLL in TSMC 40nm IP

- TSMC GF Intel Samsung Deskew Frequency Synthesizer PLL

- TSMC GF Intel Samsung Fractional-N Frequency Synthesizer PLL

- TSMC GF Intel Samsung Integer-N Frequency Synthesizer PLL

- TSMC Intel 32kHz Low-bandwidth Frequency Synthesizer PLL

- MIPI D-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)