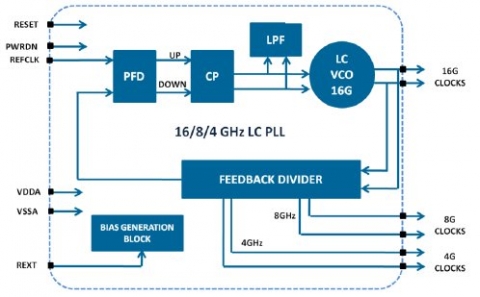

High Speed Low Jitter 16GHz Output LC PLL

A reset sequence is designed to achieve phase lock on power up or mode change.

The PLL needs a dedicated power supply to reduce the effect of supply noise on it.

The frequency output is applicable for multiple protocols.

查看 High Speed Low Jitter 16GHz Output LC PLL 详细介绍:

- 查看 High Speed Low Jitter 16GHz Output LC PLL 完整数据手册

- 联系 High Speed Low Jitter 16GHz Output LC PLL 供应商

Block Diagram of the High Speed Low Jitter 16GHz Output LC PLL

Low Jitter IP

- TSMC GF Intel Low Phase Noise, High-performance Digital LC PLL

- Low jitter 4.96GHz to 5.6GHz PLL in TSMC N40

- PCIe/HCSL Differential IO Buffer - TSMC 16FFC

- Low jitter, low-power clock-deskew PLL operating from 6GHz to 9.5GHz

- Low jitter, ultra-low power (<950uW) ring-oscillator-based PLL-2.4GHz

- 25MHz Low Jitter Low Power XTAL Oscillator with AGC