PCIe 4.0 Controller supporting Endpoint, Root Port, Switch, Bridge and advanced features

High-Performance Lossless Compression/Encryption Combo Core

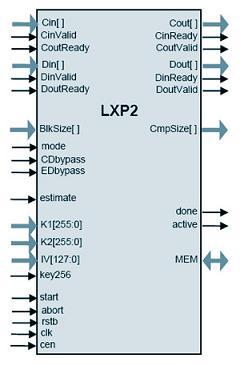

LXP2 implements the lossless compression /decompression algorithm and AES-XTS encryption /decryption on units of data (“blocks”). Typical applications include enterprise data storage.

The design is fully synchronous and available in multiple configurations varying in bus widths and throughput.

LXP2 delivers 1-3 Gbps of throughput in both FPGA and ASIC implementations. The compression ratio greatly depends on the data and somewhat depends on the frames size; on typical file corpuses varies between 1.5 and 2.

查看 High-Performance Lossless Compression/Encryption Combo Core 详细介绍:

- 查看 High-Performance Lossless Compression/Encryption Combo Core 完整数据手册

- 联系 High-Performance Lossless Compression/Encryption Combo Core 供应商

Block Diagram of the High-Performance Lossless Compression/Encryption Combo Core

Lossless compression IP

- VESA DSC (Display Stream Compression) 1.2b Video Encoder

- VESA DSC (Display Stream Compression) 1.2b Video Decoder

- ASIL-B Ready ISO 26262 Certified VESA DSC (Display Stream Compression) 1.1 Encoder

- JPEG 2000 Encoder - Up to 16-bit per Component Lossy & Numerically Lossless Image & Video Compression

- CCSDS 122.0-B-1 Encoder - Lossless and Lossy Image Data Compression with up to 16 bits Pixel Dynamic Range

- Visually LossLess compression hardware RTL core that complies with ISO/IEC-21122-1 (JPEG XS)