You are here:

High-performance 64-bit RISC-V architecture multi-core processor with AI vector acceleration engine

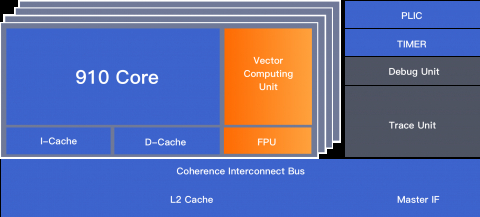

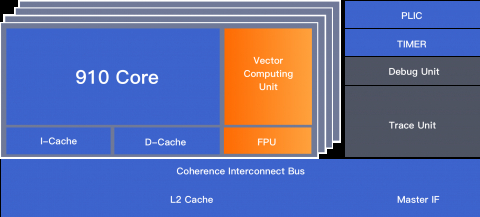

C910 utilizes a 12-stage superscalar pipeline, is compatible with RISC-V architecture, and is enhanced for arithmetic operations, memory access and multi-core synchronization. It also has a standard memory management unit and can run operation systems such as Linux. Utilizing a 3-issue and 8-execution out-of-order execution architecture, it can be equipped with a single/double-precision floating point engine. It can be further equipped with a vector computing engine for AI acceleration, making it suitable for application fields requiring high-performance, such as 5G and artificial intelligence.

查看 High-performance 64-bit RISC-V architecture multi-core processor with AI vector acceleration engine 详细介绍:

- 查看 High-performance 64-bit RISC-V architecture multi-core processor with AI vector acceleration engine 完整数据手册

- 联系 High-performance 64-bit RISC-V architecture multi-core processor with AI vector acceleration engine 供应商

Block Diagram of the High-performance 64-bit RISC-V architecture multi-core processor with AI vector acceleration engine

CPU IP

- High Bandwidth Out-of-Order RISC-V CPU IP Core

- All in one solution for AI in RISC-V

- 2D (vector graphics) GPU IP Further advanced architecture for minimized CPU load and increased pixel performance in vector processing

- 2D (vector graphics) & 3D GPU IP A GPU IP combining 3D and 2D rendering features with high performance, low power consumption, and minimum CPU load

- High Bandwidth In-Order RISC-V CPU IP Core

- RISC-V Processor - RV12 - 32/64 bit, Single Core CPU