You are here:

HDR ISP framework for multi-camera applications

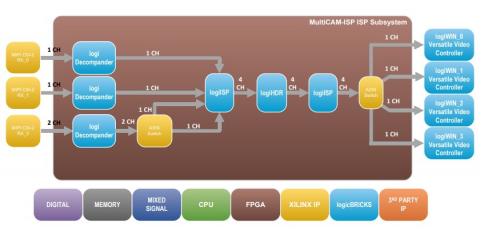

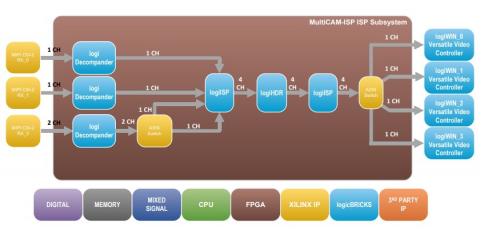

Xylon offers a complete logicBRICKS IP suite for implementing High-Dynamic Range (HDR) Image Signal Processing (ISP) pipelines in embedded designs based on Xilinx FPGA, SoC, MPSoC or ACAP programmable devices. HDR ISP pipelines enable crisp camera video under altering and rough lighting conditions in next-generation multi-channel embedded systems for use in automotive, surveillance, medical and similar video and vision AI applications.

logicBRICKS ISP IP cores enable parallel processing of multiple Ultra HD video inputs in different Xilinx devices, ranging from the small Xilinx Artix® FPGAs to the latest Xilinx Versal™ Adaptive Compute Acceleration Platform (ACAP) devices.

The logiREF-MULTICAM-ISP demonstrates these capabilities and shows how, in comparison to simple instantiation of multiple ISP pipelines within a single programmable device, Xylon’s logicBRICKS ISP pipeline allows for tremendous savings of up to 50 % of valuable programmable logic.

logicBRICKS ISP IP cores enable parallel processing of multiple Ultra HD video inputs in different Xilinx devices, ranging from the small Xilinx Artix® FPGAs to the latest Xilinx Versal™ Adaptive Compute Acceleration Platform (ACAP) devices.

The logiREF-MULTICAM-ISP demonstrates these capabilities and shows how, in comparison to simple instantiation of multiple ISP pipelines within a single programmable device, Xylon’s logicBRICKS ISP pipeline allows for tremendous savings of up to 50 % of valuable programmable logic.

查看 HDR ISP framework for multi-camera applications 详细介绍:

- 查看 HDR ISP framework for multi-camera applications 完整数据手册

- 联系 HDR ISP framework for multi-camera applications 供应商

Block Diagram of the HDR ISP framework for multi-camera applications