You are here:

HDMI 1.4 Rx PHY 和控制器 IP,在 TSMC 65/55LP 中经过硅验证

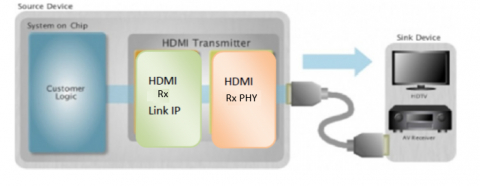

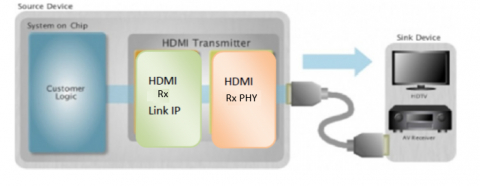

HDMI Rx PHY (物理层) IP 是单端口的 IP,完全符合 HDMI 1.4 规范。这个 HDMI RxPHY IP支持25MHz 到 225MHz 的 TMDS 时钟,提供了简单的系统 LSI 解决方案,适用于像 HDTV 这样的消费电子领域的产品。这个IP已经在多个制造工艺/节点上通过了硅验证,包括:(TSMC, UMC, SMIC, GF, Samsung, STMicro)。HDMI RX链路 IP 支持 HDMI 1.4 的标准,可以快速地实现到消费者产品的 SoC (高清电视,音频 RX等),与 HDMI RxPHY IP 协作工作时,可以实现 HDMI RX链路 IP 的最佳性能、效率和特性。这个 HDMI Rx IP 可以根据客户的具体需求进行定制

查看 HDMI 1.4 Rx PHY 和控制器 IP,在 TSMC 65/55LP 中经过硅验证 详细介绍:

- 查看 HDMI 1.4 Rx PHY 和控制器 IP,在 TSMC 65/55LP 中经过硅验证 完整数据手册

- 联系 HDMI 1.4 Rx PHY 和控制器 IP,在 TSMC 65/55LP 中经过硅验证 供应商

Block Diagram of the HDMI 1.4 Rx PHY 和控制器 IP,在 TSMC 65/55LP 中经过硅验证