You are here:

H.264 Low Power & Low Latency Hardware Video Decoder

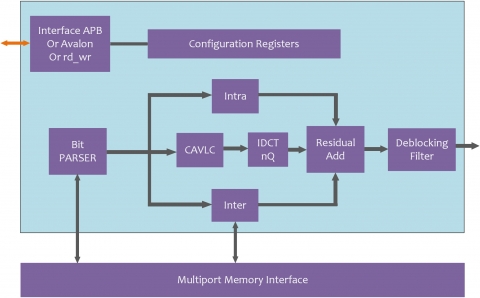

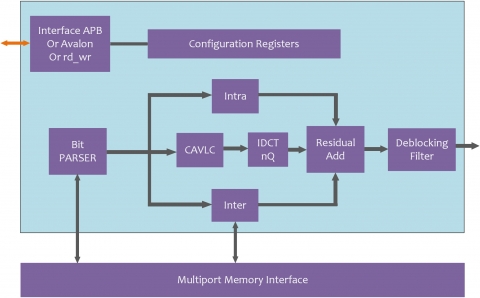

The Atria Logic AL-H264D-HW is a hardware-based, low power, low latency, feature-rich, H.264 (AVC) Baseline Profile video decoder IP core, targeted for mobile and non-mobile, low power devices in industrial, medical and CE applications. Industrial applications include remote monitoring of manufacturing plants, remote control of UAVs, and digital signage for advertising and information displays in hotels, ATMs, gas pumps, kiosks, etc. Medical applications include endoscopic, assisted surgery and remote diagnostics applications, CE applications include in-flight and automotive infotainment systems, netbooks, tablets and smartphones.

The decoder supports Baseline Profile I+P decoding up to Level 4.1 (1080p30), as well as error resiliency/robustness with Arbitrary Slice Ordering (ASO), Flexible Macroblock Ordering (FMO) and skipped macroblock support when receiving video data packets over unpredictable networks.

The decoder is fully H.264 standards compliant, with support for all 4x4 and 16x16 luma and all chroma modes, up to 16 motion vectors (i.e., all permitted block sizes) per macroblock, cross-frame boundary motion vectors, 1/2 and 1/4 pel motion compensation and a large horizontal and vertical motion vector range of +/-2048 and +/- 512, respectively. An in-loop deblocking filter is also included for enhanced video quality.

Configuration and control support of the decoder is supported via a register set which is accessible over the AMBA/AVALON bus. The RTL implementation supports a hardwired, micro-code free mode of implementation, as well as an ARM embedded processor assisted hardware-software partitioned mode of implementation.

The decoder design is based on a synchronous, positive-edge clocking scheme for easy targeting to ASIC or FPGA implementations. A clock-gated, multi-clock domain design supports very low power operation modes. For instance, 30fps CIF decode using only a 12MHz clock source. The design is easily scalable to decode multiple streams simultaneously.

The decoder supports Baseline Profile I+P decoding up to Level 4.1 (1080p30), as well as error resiliency/robustness with Arbitrary Slice Ordering (ASO), Flexible Macroblock Ordering (FMO) and skipped macroblock support when receiving video data packets over unpredictable networks.

The decoder is fully H.264 standards compliant, with support for all 4x4 and 16x16 luma and all chroma modes, up to 16 motion vectors (i.e., all permitted block sizes) per macroblock, cross-frame boundary motion vectors, 1/2 and 1/4 pel motion compensation and a large horizontal and vertical motion vector range of +/-2048 and +/- 512, respectively. An in-loop deblocking filter is also included for enhanced video quality.

Configuration and control support of the decoder is supported via a register set which is accessible over the AMBA/AVALON bus. The RTL implementation supports a hardwired, micro-code free mode of implementation, as well as an ARM embedded processor assisted hardware-software partitioned mode of implementation.

The decoder design is based on a synchronous, positive-edge clocking scheme for easy targeting to ASIC or FPGA implementations. A clock-gated, multi-clock domain design supports very low power operation modes. For instance, 30fps CIF decode using only a 12MHz clock source. The design is easily scalable to decode multiple streams simultaneously.

查看 H.264 Low Power & Low Latency Hardware Video Decoder 详细介绍:

- 查看 H.264 Low Power & Low Latency Hardware Video Decoder 完整数据手册

- 联系 H.264 Low Power & Low Latency Hardware Video Decoder 供应商

Block Diagram of the H.264 Low Power & Low Latency Hardware Video Decoder